Home Search Collections Journals About Contact us My IOPscience

High-performance N-polar GaN enhancement-mode device technology

This article has been downloaded from IOPscience. Please scroll down to see the full text article. 2013 Semicond. Sci. Technol. 28 074006 (http://iopscience.iop.org/0268-1242/28/7/074006) View the table of contents for this issue, or go to the journal homepage for more

Download details: IP Address: 128.205.187.143 The article was downloaded on 21/06/2013 at 16:12

Please note that terms and conditions apply.

Semicond. Sci. Technol. 28 (2013) 074006 (13pp)

### **INVITED REVIEW**

# **High-performance N-polar GaN enhancement-mode device technology**

#### Uttam Singisetti<sup>1</sup>, Man Hoi Wong<sup>2</sup> and Umesh K Mishra<sup>3</sup>

<sup>1</sup> Electrical Engineering Department, University at Buffalo, Buffalo, NY 14260, USA

<sup>2</sup> SEMATECH Inc., Austin, TX 78741, USA

<sup>3</sup> ECE Department, University of California, Santa Barbara, CA 93106, USA

E-mail: uttamsin@buffalo.edu

Received 30 November 2012, in final form 6 February 2013 Published 21 June 2013 Online at stacks.iop.org/SST/28/074006

#### Abstract

In this paper, we report the recent progress in the high-frequency performance of enhancement-mode devices in the novel N-polar GaN technology and provide a pathway for further scaling. The intrinsic advantages of electron confinement, polarization doping of the back-barrier and the absence of a source barrier in N-polar GaN technology were leveraged with polarization engineering with a top barrier for enhancement mode operation and advanced self-aligned source/drain technology for low parasitic access resistances. The scalability of the device structures are explored in terms of short-channel effects and high-frequency performance. Low-field electron mobility in vertically scaled channel was also investigated providing insights on the scattering mechanism.

(Some figures may appear in colour only in the online journal)

#### 1. Introduction and background

Since the first report of GaN-based light-emitting diode and high-electron mobility transistors (HEMTs) [1, 2], there has been incredible progress in GaN electronics and optoelectronics technology with a broad range of applications. The unique properties of high-electron mobility in a polarization doped two-dimensional electron gas (2-DEG) in AlGaN/GaN hetero-structure and high breakdown enabled by the large bandgap of GaN has been an attractive feature of GaN electronic devices [3]. This distinct combination leads to high-frequency and high-voltage operation in GaN devices unlike the traditional III-V and Si electronics, with orders of magnitude higher power handling capabilities in microwave and mm-wave frequencies [4-7]. Aggressive gate length scaling of GaN devices can push the device operation well into near THz operation. Due to the high-voltage operation capability of these devices, they have the potential to operate in space that is not accessible to other technologies [8].

There has been remarkable progress in high-frequency GaN field-effect transistors (FETs) in recent years enabled by aggressive gate length scaling to 20 nm and also by drastic

reduction in parasitic source resistance by incorporating source/drain regrowth with peak reported current gain cutoff frequency of 370 GHz [9-14]. In order to maintain the electrostatic integrity of the ultra-scaled devices with tight gate control of the channel, new technologies with backbarrier for electron confinement are being pursued [14–16]. The novel N-polar GaN technology where the material is grown on (000-1) axis offers a natural back-barrier, which is an attractive option for ultra-scaled devices [17, 18]. In addition to providing electron confinement, it offers several other advantages for GaN transistors for high-frequency operation. N-polar GaN FETs with a top gate dielectric and a bottom charge inducing wide bandgap AlGaN backbarrier provide a structure similar to ultrathin body siliconon-insulator (UTB-SOI) devices and hence have the potential advantage in scaling to sub-50 nm gate lengths. Moreover, the absence of a polarization inducing wide-bandgap AlGaN material on top of the channel removes the barrier to electron flow from the source contact to the 2-DEG, thus reducing the source parasitic resistance [17, 19].

Depletion-mode N-polar GaN HEMTs on molecular beam epitaxy (MBE) grown material was first reported

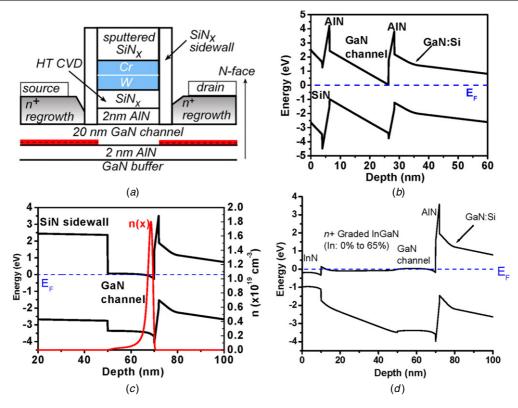

**Figure 1.** (*a*) Cross-section schematic of a self-aligned E-mode N-polar device. (*b*) Simulated band diagram and electron density of the device (*a*) under the gate showing normally off mode, (*b*) under the sidewall regions with a 2-DEG density of  $5 \times 10^{12}$  cm<sup>-2</sup>, and (*d*) under the source contact after MBE regrowth. (*a*), (*b*) and (*c*)<sup>©</sup> [2011] IEEE, reprinted, with permission from [27].

in 2007 [17]. Within a short period of time, significant progress has been made on N-polar device technology with comparable results to the more mature Ga-polar GaN HEMT technology [19–23]. Low source contact resistance and source access resistances in GaN HEMTs were first demonstrated in N-polar GaN devices by incorporating self-aligned source/drain regrowth technology [24]. In conjunction with a strain-free lattice matched InAlN back-barrier layers record high transconductance and power gain cutoff frequency has been reported [21, 25]. Thus, N-polar GaN technology has evolved as a viable candidate for ultra-scaled GaN HEMT technology. In this paper, we review the recent progress on the enhancement-mode (E-mode) N-polar GaN technology for high-frequency applications. E-mode devices are attractive due to the single voltage which simplifies the circuit topologies.

The basic device structure of an N-polar GaN HEMT consists of a GaN channel on top of a wide-bandgap  $Al_xGa_{1-x}N$  layer similar to inverted AlGaAs/GaAs HEMT. The inherent polarization from the back-barrier in N-polar devices leads to a 2-DEG in the GaN channel and a normally on depletion mode operation. If a wide-bandgap AlGaN layer is grown on top of the channel, the negative polarization charge at the top interface will deplete the 2-DEG. If sufficient negative polarization charge is induced either by increasing Al composition or thickness of the wide bandgap  $Al_xGa_{1-x}N$  layer, the 2-DEG can be completely depleted and an enhancement-mode device can be obtained. Besides the negative polarization charge for enhancement-mode operation, other considerations such as strain relaxation, gate capacitance, ease of etching and

etch selectivity will be crucial in designing the top barrier layer. Using AlN top-layer for enhancement-mode operation has the advantages of low thickness that increases the gate capacitance which also at the same time has the potential to offer highest selectivity in etch rates between AlN and GaN.

Removing the top 2-DEG depleting AlN layer in the access regions recovers the 2-DEG which will reduce the access resistance. In addition, highly doped source/drain regions can be grown to further reduce the access resistance [26]. In the next section, we report on the details of devices design and fabrication of self-aligned N-polar GaN enhancement-mode devices.

#### 2. First generation of E-mode devices

The first generation of E-mode devices reported was on a 20 nm thick GaN channel with self-aligned source/drain regrowth [27, 28]. A schematic cross-section of the self-aligned device structure is shown in figure 1(a). The device utilized a gate-first refractory metal process with self-aligned source drain regions by MBE regrowth. Figure 1 also shows the simulated band-diagrams of the various regions of the device. Under the gate, the band-diagram shows that the 2-DEG is completely depleted by the top AlN layer and the device will be normally off. In the sidewall access regions, where the top AlN layer is removed and plasma-enhanced chemical vapor deposition (PECVD) SiN<sub>x</sub> is deposited the 2-DEG is recovered in the GaN channel. In the source/drain regions a graded InGaN/InN regrowth is carried out after gate formation, the simulated band-diagram

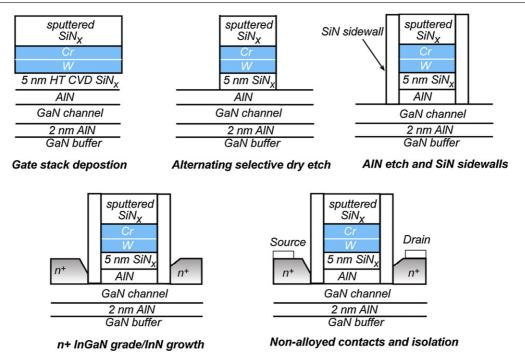

Figure 2. Self-aligned N-polar GaN device fabrication process. The gate etch process was adapted from III-V MOSFET process in [29].

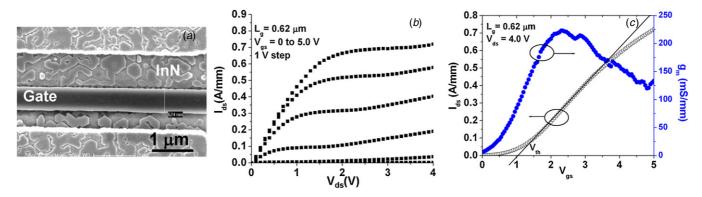

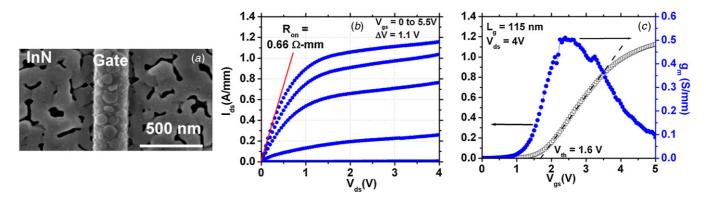

**Figure 3.** (*a*) SEM imgage of the device showing InN growth next to gate. (*b*) dc output, and (*c*) dc input characateristics of a 0.62  $\mu$ m gate length device. <sup>©</sup> [2011] IEEE, reprinted, with permission from [27].

shows that there is no barrier to electrons from the source contact to the channel [24, 26].

All the device structures reported here were grown by plasma-assisted MBE. The 20 nm GaN channel device structure was grown on C-face SiC substrates to obtain N-polarity. An AlN nucleation layer followed by a twostep GaN buffer was adopted for growing a high-quality, semi-insulating buffer. After the device was grown, 5 nm of  $SiN_x$  was deposited on top by high-temperature chemical vapor deposition (HT-CVD) for the gate barrier. Next a composite  $W/Cr/SiN_x$  gate stack was deposited; W and  $SiN_x$ were deposited by Ar-sputtering and the Cr was deposited by electron beam evaporation. The gate stack process was adapted from III-V MOSFET process reported in [29], with the top SiO<sub>2</sub> layer replaced by Ar-sputtered SiN<sub>x</sub> layer for etch selectivity with the HF-based wet etch process for the top-AlN layer. The composite  $W/Cr/SiN_x$  gates were defined by electron beam lithography and selective dry etches with gate lengths varying from 10 to 0.18  $\mu$ m.

The device fabrication process is shown in figure 2. After the gate definition, the AlN layer in the access regions was selectively wet etched by UV-Ozone oxidation followed by buffered HF etch [28]. This etch selectively removes the AlN layer stopping on the GaN channel layer. The high selectivity of the etch enables an over etch of AlN layer without the danger of etching the thin GaN channel layer. Before source/drain regrowth, SiN<sub>x</sub> sidewalls were defined by a low-power reactive ion etch. The source/drain regions were grown by plasmaassisted MBE [26]. After the regrowth, non-alloyed Ti/Au source/drain contacts were formed and the devices were mesa isolated by reactive ion etching.

Figure 3(*a*) shows a scanning electron microscope (SEM) image of a device after regrowth, which shows the InN growth next to gate. The dc characteristics of the device are shown in figures 3(*a*) and (*b*). The device clearly shows an enhancement-mode operation with a linearly extrapolated threshold voltage ( $V_t$ ) of 1.0 V, which was expected from the simulated band-diagrams of the device structure. The deposition of SiN<sub>x</sub> gate

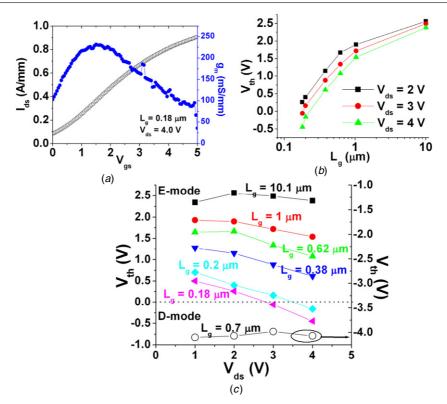

**Figure 4.** (*a*) Input characteristics at  $V_{ds} = 4.0$  V for a 0.18  $\mu$ m length devices. (*b*) Threshold voltage roll off with decreasing gate length and (*c*) increasing drain bias. The open circles (right *y*-axis) in (*c*) show the  $V_{th}$  for a non-self-aligned D-mode device. <sup>©</sup> [2011] IEEE, reprinted, with permission from [27].

dielectric does not lead to a depletion mode device which was observed in Ga-polar devices [30]. The maximum drain current  $(I_d)$  and maximum transconductance  $(g_m)$  of the device were 0.74 A mm<sup>-1</sup> and 225 mS mm<sup>-1</sup>, respectively.

The gate length scalability of the device structure was investigated with respect to dc device performance. As the gate length is reduced, the devices show threshold voltage roll-off with the 0.18  $\mu$ m gate length device showing a depletion mode operation (figure 4(*a*)). The threshold voltage dependence on gate length and drain bias is shown in figure 4. As seen in figure 4, the threshold voltage decreases with increasing drain bias for a given gate length device. It also decreases with decreasing gate length at a given drain bias. Drain-induced barrier lowering (DIBL) is the reason for the observed V<sub>t</sub> rolloff, which has been observed in Ga-polar E-mode devices [31]. However, the roll off observed in these devices is faster than that reported in Ga-polar HEMTs [32]. The V<sub>t</sub> roll off is also faster than depletion-mode N-polar devices with nonself-aligned devices as shown in figure 4(*c*).

The aspect ratio of the device dictates the FET electrostatics and DIBL effect [33]. The aspect ratio  $(L_g/t_{bar})$  of the 0.18  $\mu$ m device is 6.7, a low value at which the short channel effects are expected [33]. In addition, N-polar GaN devices show poor dc saturation and DIBL effect arising from traps in the back barrier [34, 34]. The E-mode devices here show enhanced  $V_t$  roll off because of the self-aligned drain structure. The self-aligned drain leads to a more intrinsic drain voltage that enhances the DIBL effect. Such enhanced DIBL effect has been reported in Si metal-oxide semiconductor FETs (MOSFETs) [36].

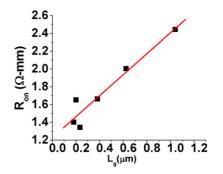

**Figure 5.** Device on resistance versus gate length. A total source/drain parasitic access resistance of 1.2  $\Omega$ -mm is extracted from the linear interpolation to zero gate length. <sup>©</sup> [2011] IEEE, reprinted, with permission from [27].

Figure 5 shows the variation of the device on-resistance with gate length. The extrapolated source access resistance is 0.6  $\Omega$ -mm. In order to evaluate the components of the source resistance, transfer length method (TLM) structures were measured on the regrown InN/InGaN layer, which give a sheet resistance and contact resistance of 540 Ohm/ $\Box$  and 0.04  $\Omega$ -mm, respectively. The contribution of the 50 nm SiN<sub>x</sub> sidewall region is calculated from the measured sheet resistance of the SiN<sub>x</sub>/GaN process monitor sample. The total source access resistance calculated from the test structures is 0.51  $\Omega$ -mm, while the extrapolated resistance is 0.6  $\Omega$ -mm. The difference of 0.09  $\Omega$ -mm is the contribution from the regrowth interface resistance. The regrowth interface resistance can be further reduced to the fundamental limit as reported in [37].

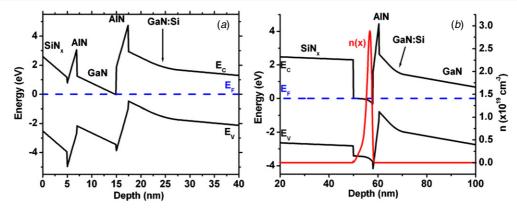

**Figure 6.** Band diagram for the 8 nm thick GaN channel device (*a*) under the gate showing E-mode operation. (*b*) Under the SiN<sub>x</sub> sidewall access region.).  $^{\odot}$  [2011] The Japan Society of Applied Physics, reprinted, with permission from [38].

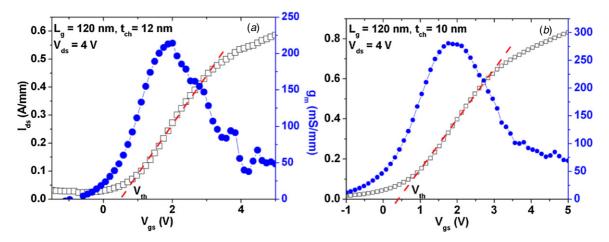

Figure 7. DC input characteristics of a 120 nm gate length device with (*a*) 12 nm thick GaN channel and (*b*) 10 nm thick GaN channel. Both devices show a linearly extrapolated positive threshold voltage.

The OFF state performance of the device shows severe limitations. The ON–OFF ratio of the 0.62  $\mu$ m devices is 720, which degrades to 10 for the 0.18  $\mu$ m devices. The three-terminal breakdown of the 0.62  $\mu$ m device is 15 V, which is low compared to the non-self-aligned devices. The self-aligned structure with higher intrinsic drain voltage leads to lower breakdown than a non-self-aligned device. An offset drain voltage structure with lower drain doping will increase the breakdown voltage.

In summary, the first generation of E-mode devices with 20 nm thick GaN channel show good dc performance. However, due to the low aspect ratio the device gate lengths cannot be scaled beyond 0.18  $\mu$ m while maintaining a positive  $V_t$ . In order to maintain E-mode operation in ultra-scaled device, the devices' vertical dimension has to be reduced to increase the aspect ratio.

#### 3. Vertical scaling of the GaN channel

In order to reduce the gate transit time and obtain high frequency operation in N-polar GaN devices, the gate length has to be scaled along with the vertical dimensions of the device. In this section, we summarize the results of vertical scaling of the GaN channel in E-mode N-polar devices [38].

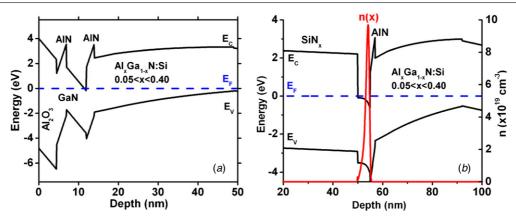

The device design goals for vertically scaled channel structures are E-mode operation under the gate and high charge density under the sidewall regions which have opposite requirements on the back-barrier doping density. A higher polarization doping would increase the conductivity of the sidewall access regions; however, the larger value will require a thicker AlN layer to deplete the 2-DEG which may crack due to strain. The proximity of the surface in scaled channels provides a challenge in device design because it has direct impact on the 2-DEG charge density and electron mobility. Keeping these constraints in mind, we designed three devices with GaN channel thickness of 12 nm, 10 nm and 8 nm, respectively. The simulated band diagrams for the 8 nm thick GaN channel device under the gate and under the sidewall are shown in figure 6. The simulated 2-DEG concentrations under the sidewall regions for the 12 nm, 10 nm and 8 nm thick GaN channel devices are 6.6  $\times$  10<sup>12</sup>, 7.6  $\times$  10<sup>12</sup> and  $9.7 \times 10^{12} \,\mathrm{cm}^{-2}$ , respectively.

Self-aligned FETs were fabricated on these samples with electron beam lithography (EBL)-defined gates following the process described in the previous section. The dc characteristics of 0.12  $\mu$ m gate length devices with 12 nm and 10 nm GaN channel thickness are shown in figure 7. As seen in the figure, both devices have positive threshold voltage, while similar gate length devices with 20 nm thick

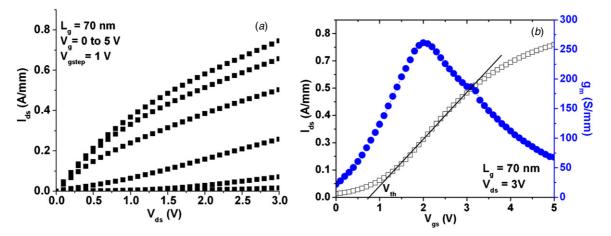

Figure 8. Common-source output and input characteristics of the 70 nm gate length device with 8 nm thick GaN channel. <sup>©</sup> [2011] The Japan Society of Applied Physics, reprinted, with permission from [38].

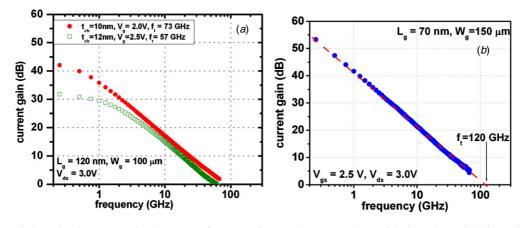

**Figure 9.** Measured short circuit current gain ( $h_{21}$ ) versus frequency for (*a*) 12 nm and 10 nm thick GaN channel devices with gate length of 120 nm, and (*b*) 8 nm thick GaN channel device with a gate length of 70 nm. A current gain cut off frequency ( $f_t$ ) of 120 GHz is extrapolated. (*b*) <sup>©</sup> [2011] The Japan Society of Applied Physics, reprinted, with permission from [38].

GaN channel were depletion mode with negative threshold voltages. The increased aspect ratio helps maintain the positive  $V_t$  till 0.12  $\mu$ m. However, these devices still show gate length dependent and drain voltage dependent threshold voltages. Both the 12 nm and 10 nm GaN channel devices become depletion-mode at a gate length of 70 nm (not shown).

On further scaling of the GaN channel thickness to 8 nm, E-mode operation with positive  $V_t$  is obtained for 70 nm gate length device. The dc output and input characteristics of the device is shown in figure 8. The peak current and peak transconductance of the device are 0.74 A mm<sup>-1</sup> and 260 mS mm<sup>-1</sup>, respectively, with a linearly extrapolated positive threshold voltage of 0.7 V at  $V_{ds} = 3.0$  V.

The high-frequency performance of these devices was characterized by measuring the s-parameters on Agilent E8316A PNA from 100 MHz to 67 GHz. The PNA was first calibrated using Cascade Microtech LRRM standard, which brings the measurement reference plane to the probe tips. In order to de-embed the device pad parasitics and determine the intrinsic device performance, on-wafer openshort pads were measured after calibration. The intrinsic device s-parameters were determined by de-embedding the pad reactance calculated from the on-wafer open-short test structures [39]. The small-signal current gain versus frequency for the 12 nm and 10 nm thick GaN channel E-mode devices is shown in figure 9(*a*). The peak current gain cut-off frequency ( $f_t$ ) for the 12 nm and 10 nm thick GaN channel devices is 57 and 73 GHz, respectively. The higher  $f_t$  for the 10 nm thick channel device is due to the higher transconductance compared to the 12 nm thick channel that results from increased gate capacitance.

The small-signal performance of the 8 nm thick channel device is shown in figure 9(*b*). The peak  $f_t$  is 120 GHz. Scaling the channel thickness ensures positive  $V_t$  and also increases the  $f_t$  due to increased gate capacitance. The power-gain cut off frequency of all the three devices reported here was low due to the high gate resistance of the thin W gate metal layer.

Despite excellent high frequency operation in these devices, they show poor dc saturation. The principle cause for this is the device structure. The device structure has been found to have direct impact on the dc output conductance of an N-polar HEMT [35]. The abrupt junction device structure used in this study has the highest dc output conductance resulting from traps at the bottom interface [35]. The device structure in combination with the self-aligned structure results in the observed high dc output conductance. This trap-induced dc

\* 2 X of 5 minute UV-Ozone-30sec-BHF

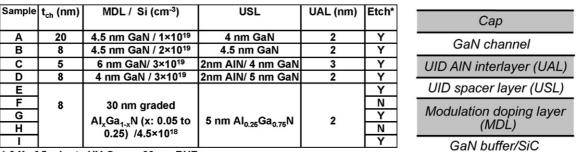

Figure 10. Details of the N-polar structures for transport study. All the samples except for H and I had 40 nm of PECVD  $SiN_x$  cap.

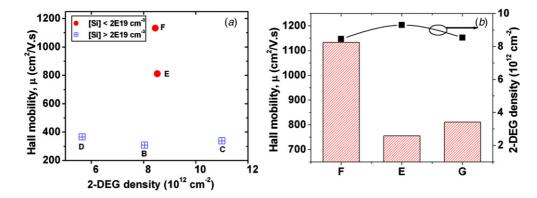

**Figure 11.** (*a*) Hall mobility and 2-DEG density of samples B to F. High 3-D Si doping leads to low mobility in B, C and D. (*b*) Hall mobility and 2-DEG density of 8-nm GaN channel samples with (E, G) and without (F) exposure to UV-Ozone-BHF treatment.

output conductance does not impact the RF output conductance values. Separation of trap induced and short channel dc output conductance in these devices will require extensive modeling. The future devices incorporated a graded back-barrier design in order to reduce the impact of this trap [35] and also improve mobility.

The on-resistance in these scaled channel devices reported in this section was high compared to the 20 nm thick GaN channel devices in the previous section. The contact resistance measured from TLMs for the 12 nm and 10 nm thick GaN channel device was 0.02  $\Omega$ -mm, while the TLM did not show a linear response due to inhomogeneous growth for the 8 nm GaN channel device resulting only in partial coverage of InN near the gate. The growth of InN is very sensitive to actual temperature with a narrow window of growth [40].

Besides the regrowth resistance, the sidewall access resistance in these samples was also high due to surface effects. The measured sidewall region mobility in thin 8 nm channel devices was  $350 \text{ cm}^2/\text{V.s}$ , which was lower than the mobility of  $1060 \text{ cm}^2/\text{V.s}$  in a 20 nm thick channel device. Systematic mobility studies were carried out to understand the scattering mechanisms.

#### 4. Mobility in N-polar quantum well channels

The mobility in the vertically scaled GaN channels needs to be high in order to reduce the access resistance and also to ensure that the device achieves ballistic operation [41]. The sidewall access region conductivity in the self-aligned N-polar FETs is determined by the 2-DEG density and mobility. The access region is exposed to various fabrication processes such as UV-Ozone-HF etch and PECVD deposition that can adversely impact the 2-DEG density and mobility. In addition, the device structure will also influence the scattering mechanisms and mobility. The GaN channel in N-polar GaN devices is a double hetero-structure quantum well, which will influence the electron scattering mechanism. In order to gain insight into mobility-limiting mechanisms, a systematic study was carried out.

Figure 10 gives the list of device structures studied to separate the contribution of the device structure and the fabrication process to electron scattering. The basic device structure consists of a modulation doping layer, a setback and an AlN interlayer. The modulation doping layer, in addition to proving electrons to the 2-DEG, moves the Fermi-level away from the valence band that removes the high-frequency dispersion and improves dc output resistance [17, 35].

Hall mobility was measured on these samples in the Vander Pauw geometry with In contacts. In figure 11, the mobility of 5 nm and 8 nm thick GaN channels is seen to depend on the back-barrier modulation doping density. The devices with high three-dimensional (3D) Si doping ( $>2 \times 10^{19}$  cm<sup>-3</sup>) density have lower mobility than devices with lower 3-D density. Higher Si doping density could lead to higher roughness and hence lower mobility. As a result the graded AlGaN backbarrier layer leads to higher mobility, as this requires lower 3-D Si doping in order to keep the Fermi-level away from the valance band to reduce the high-frequency dispersion. The mobility also depends on the process history of the sample. The samples with UV-ozone-BHF etch show a degradation of

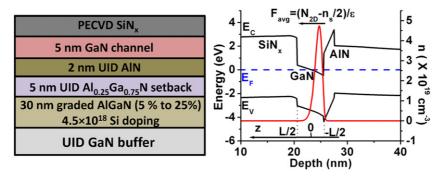

**Figure 12.** (*a*) The layer structure schematic and (*b*) simulated band diagram and electron density of the 5 nm GaN channel device. The UID in the AlN inter layer is  $1 \times 10^{18}$  cm<sup>-3</sup>, the doping in the AlGaN graded layer is  $4.5 \times 10^{18}$  cm<sup>-3</sup>. Reprinted from [42]. <sup>©</sup> 2012, American Institute of Physics.

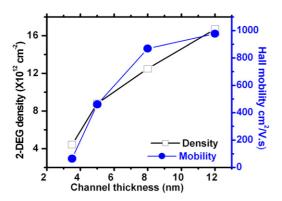

**Figure 13.** Measured room temperature Hall mobility and 2-DEG density as a function of GaN channel thickness. Reprinted from [42]. <sup>©</sup> 2012, American Institute of Physics.

mobility. This etch is selective to GaN; however, it can roughen the GaN surface to reduce the mobility.

In order to quantify the scattering mechanisms we carried out a theoretical and experimental investigation of gradedback barrier samples that were not exposed to UV-ozone etch [42]. The device structure (figure 12) consists of a top GaN channel, a 2 nm AlN back-barrier which reduces the alloy scattering rate of the 2-DEG, a 5 nm un-intentionally doped Al<sub>0.25</sub>Ga<sub>0.75</sub>N setback layer, a 30 nm graded AlGaN modulation doping layer ((Si) =  $4.5 \times 10^{18}$  cm<sup>-3</sup>) and a GaN buffer. Four samples with channel thicknesses of 12 nm, 8 nm, 5 nm and 3.5 nm were grown within a short period of time to minimize any drift in the device material quality; all of them have the same layer structure shown in figure 12. The devices were grown by plasma-assisted molecular beam epitaxy (PA-MBE) on C-face SiC. For Hall measurement purpose, the devices were diced into 7 mm  $\times$  7 mm square pieces. Next, the native surface oxide was removed with 1 minute buffered hydro-fluoric acid (BHF) treatment before deposition of 50 nm of silicon nitride  $(SiN_x)$  by plasma-enhanced chemical vapor deposition (PECVD). Annealed indium contacts were formed at the corners of the square pieces for Hall measurement.

The variation of the 2-DEG density and Hall mobility at room temperature (RT) with thickness of the GaN channel is shown in figure 13. Both the 2-DEG density and the Hall mobility decrease with channel thickness resulting in a very low mobility of 65 cm<sup>2</sup>/V.s for the 3.5 nm channel device. The Fermi-level pinning at the SiN<sub>x</sub>/GaN interface [43] leads

**Figure 14.** Measured Hall mobility as a function of temperature for the 12 nm, 8 nm and 5 nm channels. The inset shows the measured Hall mobility for the 3.5 nm channel device. Reprinted from [42]. <sup>©</sup> 2012 American Institute of Physics.

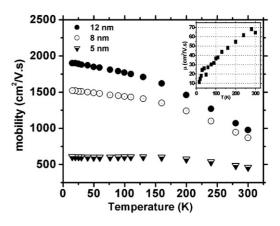

to increased depletion of the 2-DEG in thinner channels. In order to quantify the mobility-limiting mechanism in thin channels, temperature-dependent Hall mobility measurement was carried out for the samples. Figure 14 shows the measured Hall mobility for all the samples from 15 K to room temperature (300 K).

The mobility variation of the 12 nm, 8 nm and 5 nm samples shows similar behavior of increasing mobility with decreasing temperature and then saturation, while the 3.5 nm channel device shows a distinct trend of decreasing mobility with decreasing temperature. Reduced phonon population at low temperatures leads to a reduction in optical and acoustic phonon scattering rates that subsequently increase the mobility as observed for the 12 nm, 8 nm and 5 nm samples. However, the low temperature mobility saturated at a relatively lower value of <2000 cm<sup>2</sup>/V.s as compared to Ga-polar GaN HEMTs. This suggests a temperature-independent Coulombic scattering mechanism as the limiting scattering phenomenon in these devices. It is noted that the 2-DEG density remained unchanged from RT to 15 K in all the samples.

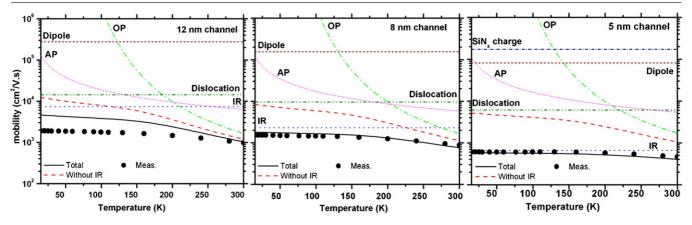

To quantify the mobility-limiting mechanisms, we calculated the 2-DEG mobility in the relaxation time approximation and in the electric quantum limit of ground state sub-band occupancy. The scattering mechanisms considered are interface roughness (IR), optical phonon (OP) scattering, acoustic phonon (AP) scattering, ionized

**Figure 15.** Calculated and measured mobilities for the 12 nm, 8 nm and 5 nm channel device. The dislocation density is assumed to be  $1 \times 10^{10}$  cm<sup>-2</sup> with a filling factor f = 0.5, the trapped charge in the SiN<sub>x</sub> is assumed to be  $1 \times 10^{13}$  cm<sup>-2</sup>, the optical phonon energy for GaN is 92 meV and the deformation potential for acoustic phonons is 9.1 eV. For IR scattering,  $\Delta = 0.48$  nm and  $\Lambda = 3.0$  nm is used for all the samples. The roughness parameters of the top and bottom interfaces are assumed to be same and uncorrelated. The  $F_{avg}$  for 12 nm, 8 nm, 5 nm and 3.5 nm samples are 1.25 MV cm<sup>-1</sup>, 1.67 MV cm<sup>-1</sup>, 2.0 MV cm<sup>-1</sup>, and 2.34 MV cm<sup>-1</sup> respectively. Reprinted from [42]. <sup>©</sup> 2012, American Institute of Physics.

impurity scattering (II), scattering due to charged dislocations, scattering due to un-intentional doping (UID) in the AlN interlayer, and scattering due to trapped charges in the PECVD  $SiN_x$ . The interface roughness scattering has not been previously considered in N-polar device structures.

Unlike the roughness scattering calculation GaAs quantum wells [44, 45] the quantum well devices studied here have a high transverse electric field ( $\sim$ MV cm<sup>-1</sup>) in the channel arising from the polarization in the wurtzite III-N system. We use a variational wavefunction for an electron confined in a quantum well with an electric field (F) which is given by [46, 47]

$$\psi(z) = N(\beta) \cos\left(\frac{\pi z}{L}\right) \exp\left(-\beta\left(\frac{z}{L} + \frac{1}{2}\right)\right), \ |z| < L/2,$$

(1)

where *L* is the channel thickness, *z* axis is in the direction growth,  $N^2(\beta) = 4\beta(\beta^2 + \pi^2) \exp(2\beta) / L\pi^2 (\exp(2\beta) - 1)$  is the normalization constant, and  $\beta$  is the variational parameter that depends on the electric field in the channel. Using this wavefunction, we calculate the interface roughness scattering rate as [42]

$$\frac{1}{\tau_{IR}} = \frac{2\Delta^2 \Lambda^2 m^*}{\hbar^3} \left( \frac{eF}{2} + \frac{\hbar^2 \pi^2}{m^* L^3} \right)^2 \times \int_0^1 \frac{u^4 \exp\left(-u^2 \Lambda^2 k_F^2\right)}{\left(u + G(q) \frac{q_{TF}}{2k_F}\right)^2 \sqrt{1 - u^2}} du$$

(2)

where  $\Delta$  and  $\Lambda$  are the Gaussian roughness parameters,  $k_F$  is the Fermi wave vector, q is the difference in the initial and final electron momentum vectors,  $u = q/k_F$ ,  $q_{\text{TF}}$  is the Thomas–Fermi screening vector, and G(q) is the form factor for screening due to the finite width of the 2-DEG. We use Price's approximation [48] for G(q) which is given by  $G(q) \cong 1/(1 + bq)$  where  $\mathbf{b} = (\int 2\psi^2 dz)^{-1}$ .

A form factor F(q),  $F(q) = \int_{-\infty}^{+\infty} \psi^2(z) \exp[q|z-d|] dz$ due to the finite width of 2-DEG wavefunction is used where *d* is the distance of the delta doping from the 2-DEG for Coulombic scattering. The alloy scattering is negligible in these devices because the 2 nm thick AlN interlayer with a large conduction band offset with GaN quenches the wavefunction rapidly with an extremely low probability of the wavefunction in the AlGaN alloy layer.

The scattering rates were calculated numerically and the total mobility was calculated using Matthiessen's rule. For the variational waveform calculation, the electric field in the channel was taken as the average electric field given by  $F_{\text{avg}} = e(N_{2D} - n_s/2)/\varepsilon_{GaN}$ , where  $n_s$  is the measured 2-DEG density, and  $N_{2D}$  is the total integrated Si (2D) doping density.

Figure 15 shows the measured and calculated mobility for the 5 nm, 8 nm and 12 nm GaN channels as a function of the temperature. Roughness parameters of  $\Delta = 0.48$  nm and  $\Lambda =$ 3.0 nm were used to fit the low temperature mobility of the 8 nm channel. The same values of  $\Delta$  and  $\Lambda$  were used for 5 nm and 12 nm samples. The  $\Delta$  value of 0.48 nm used to fit the data here is larger than the typical values in Ga-polar GaN HEMTs [49]. The inverted N-polar HEMT structure where the GaN channel is grown on an AlN layer with an underlying Si doping layer could be the reason for larger values similar to the higher roughness observed in inverted AlGaAs/GaAs HEMTs. The root mean square (rms) surface roughness measured by atomic force microscopy (AFM) of the wafers grown under similar conditions with a similar layer structure was 0.6–0.8 nm, which is again higher than typical Ga-polar GaN HEMTs.

The roughness scattering increases rapidly as the GaN channel thickness is reduced from 12 to 5 nm as shown in the calculated scattering rates in figure 15. The roughness scattering has two components as shown in equation 2: (i) the first component with  $F^2$  dependence is similar to the roughness scattering in Si MOSFETs [50] and (ii) the second component with  $L^{-6}$  dependence is similar to the roughness scattering reported for GaAs quantum wells [44]. Both these components of the roughness scattering increase with decreasing channel thickness. When the channel thickness was reduced, the 2-DEG density in the channel decreases due to the depletion from the surface pinning at the SiN<sub>x</sub>/GaN interface that

**Figure 16.** (*a*) The simulated band diagram under the gate. The thickness of the grade is 30 nm, and the Si modulation doping in the grade is  $6 \times 10^{18}$  cm<sup>-3</sup>. There is 5 nm of unintentionally doped (UID) Al<sub>0.40</sub>Ga<sub>0.60</sub>N between the modulation doped layer and the AlN back-barrier. (*b*) The simulated band diagram under the SiN<sub>x</sub> sidewall access region. <sup>©</sup> [2012] IEEE, reprinted, with permission from [51].

Figure 17. (a) SEM of InN regrowth coverage near the gate for the optimized InN regrowth condition for devices reported in this letter. dc (b) output and (c) input characteristics of the 115 nm gate length device.  $^{\circ}$  [2012] IEEE, reprinted, with permission from [51].

results in an increase in the average field in the channel. This increased field subsequently leads to higher roughness scattering due to the  $F^2$  dependence. The second component of roughness scattering also increases rapidly for channel thickness of 5 nm due to the  $1/L^6$  dependence. The discrepancy between the calculated and measured low temperature mobility of the 12 nm sample could be due to the non-inclusion of the second sub-band occupation in the mobility calculations, which is highly likely due to the large 2-DEG density of  $1.7 \times 10^{13}$  cm<sup>-2</sup>.

The measured mobility variation for the 3.5 nm sample was different from the other samples, with decreasing mobility with decreasing temperature. While the model predicts (not shown in figure 15) a constant mobility of 100  $cm^2/V.s$ with decreasing temperature. This trend of mobility with temperature can be explained by strong localization of electrons in the channel due to the high roughness. The localization leads to hopping-type conduction which is a thermally activated process and hence the mobility decreases with decreasing temperature. This further validates that the roughness is an issue in the structures studied here. This is an Anderson metal-insulator transition phenomenon [50]. From the expression for the roughness scattering it is clear that the mobility can be increased by decreasing the electric field in the channel and having smoother interfaces. The calculated RT mobility for the 3.5 nm GaN channel device with

$1 \times 10^{13}$  cm<sup>-2</sup> 2-DEG density (i.e. reduced depletion from the SiN<sub>x</sub>/GaN interface states) and  $\Delta = 0.1$  nm is 1250 cm<sup>2</sup>/V.s which is reasonably high for the ultra-thin quantum well channel FETs.

In summary, we have studied the dependence of mobility in N-polar GaN quantum well channels with thickness and have shown that roughness is the principal reason for lower mobility in the thin channels. The roughness leads an Anderson metal-to-insulator transition in the 3.5 nm channel device.

## 5. Graded AlGaN back-barrier devices with 5 nm GaN channel

Building upon the knowledge gained from the previous studies, we designed a 5 nm GaN channel device that will be scalable to sub-50 nm dimensions and maintain E-mode operation. The device structure is shown in figure 16 [51]. It incorporates a graded AlGaN back-barrier to reduce the dc output conductance arising from the trap at the back-barrier, and also to improve the mobility. The gate barrier was  $Al_2O_3$  high-k dielectric deposited by atomic layer deposition (ALD). Self-aligned devices with EBL-defined W/Cr/SiN gates were fabricated. The smallest gate length was 115 nm.

The dc characteristics of a 115 nm gate length FET shows (figure 17) a maximum  $I_d$  of 1.15 A mm<sup>-1</sup> at V<sub>gs</sub> = 5.5 V and

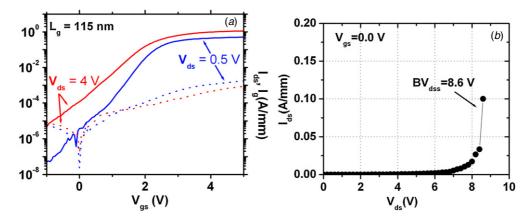

**Figure 18.** Plot of log  $I_{ds}$  versus  $V_{gs}$  and log  $I_g$  versus  $V_{gs}$  for a drain bias of 0.5 V and 4.0 V, respectively, (*b*) breakdown characteristics of the device at  $V_{gs} = 0$  V. <sup>©</sup> [2012] IEEE, reprinted, with permission from [51].

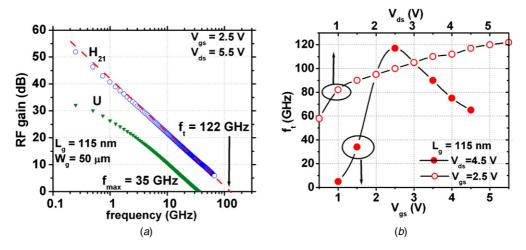

**Figure 19.** (*a*) RF gains of the device versus frequency of the device shown in figure 2. A  $f_t$  of 122 GHz and  $f_{max}$  of 35 GHz is extrapolated. (*b*)  $f_t$  versus gate voltage for  $V_{ds} = 4.5$  V (bottom *x*-axis, filled circles), and  $f_t$  versus drain bias for  $V_{gs} = 2.5$  V (top *x*-axis, open circles). <sup>®</sup> [2012] IEEE, reprinted, with permission from [51].

$V_{ds} = 4.0$  V, and a peak  $g_m$  of 510 mS mm<sup>-1</sup> at  $V_{gs} = 2.5$  V and  $V_{ds} = 4.0$  V. A positive threshold voltage of 1.6 V is extracted from the linear extrapolation of the  $I_d$ - $V_g$  plot, which is larger than the previous E-mode devices. This device structure is expected to maintain positive  $V_t$  at sub-50 nm devices.

The on resistance ( $R_{on}$ ) of the device is 0.66  $\Omega$ -mm. The low  $R_{on}$  is achieved due to a number of improvements in the device structure and regrowth process. In order to reduce the access resistance, the Si doping in the InGaN regrowth was increased to  $>1 \times 10^{20}$  cm<sup>-3</sup>. In addition, the regrowth condition for InN was optimized to get complete coverage near the gate (figure 17(a)) compared to the previously reported E-mode devices (figure 3(a)). Complete coverage of InN is ensured with a lower 450 °C regrowth temperature to reduce decomposition and increase the InN growth time. The surface Fermi-level pinning of the InN is within the conduction band and thus reduces the depletion of electrons in the device access regions [26]. Transmission line measurements (TLM) on the regrowth region gave a low sheet resistance of 100  $\Omega/\Box$  for the n<sup>++</sup> InGaN/InN regrowth layer, and a lateral contact resistance of 5  $\Omega$ - $\mu$ m between Ti and InN. The sidewall access resistance was also reduced due to the increase in the 2-DEG conductivity of the channel under the sidewall, and also by decreasing the sidewall thickness to 30 nm. A sheet resistance of 490  $\Omega/\Box$  is measured for the sidewall regions on a process monitor sample with a 2-DEG density ( $n_s$ ) of  $1.7 \times 10^{13}$  cm<sup>-2</sup> and Hall mobility of 750 cm<sup>2</sup>/V.s.

Due to the reduced effect of the trap in the graded backbarrier design, the pinch-off and the dc output resistance of the device are significantly better than the previously reported Emode devices in sections 2 and 3. Figure 18 shows that at  $V_{ds} =$ 4.0 V, the  $I_{on}$  ( $V_{gs} = 5.0$  V)/ $I_{off}$  ( $V_{gs} = 0.0$  V) is 1.16 × 10<sup>4</sup>, while the  $I_{on}/I_{off}$  is 74 for the devices reported in [7] under similar bias conditions. The three-terminal breakdown of the device is 8.6 V at  $V_{gs} = 0$  V. At  $V_{ds} = 4.0$ , the maximum  $I_{on}/I_{off}$  is 2.2 × 10<sup>5</sup>, the off-state leakage limited by the gate leakage at  $V_{gs} = -1$  V. Lower sub-threshold swing and leakage currents can be achieved by improving the dielectricsemiconductor interface.

Small-signal RF measurement of the device was performed on an Agilent E8361A PNA. After de-embedding the pad parasitics, the peak current gain cut-off frequency of the device is 122 GHz (figure 19) with an  $f_t$ - $L_g$  product of 14 GHz- $\mu$ m at a gate bias of 2.5 V and a drain bias of

5.5 V. If the same  $f_t$ - $L_g$  is maintained, a  $f_t$  of 280 GHz could be achieved at 50 nm gate length. The improvement in  $f_t$ - $L_g$ product for this device is because of the low source access resistance and higher output resistance which are the results of the optimized regrowth condition and graded back-barrier design, respectively. Figure 19(*b*) shows the variation of  $f_t$  with gate bias and drain bias.

A small-signal model of the transistor was developed. The extracted gate-drain capacitance ( $C_{gd}$ ) was 140 fF mm<sup>-1</sup> which is larger than the value reported in a non-self-aligned device [52]. Removing the drain sidewall will reduce the feedback capacitance and increase the  $f_t$  [20]. A thick low-k dielectric drain sidewall can also be used to reduce this delay, which will also improve the breakdown voltage.

#### 6. Conclusion

In conclusion, we have reported on the challenges and the recent progress in the N-polar E-mode technology. The scalability of the device structures was explored. The self-aligned devices show enhanced short-channel effects compared to non-self-aligned devices. In order to mantain E-mode operation at sub-50 nm gate lengths, the devices have to be vertically scaled to channel thickness of 5 nm. The device structure is also shown to impact the dc characteristics. The graded AlGaN back-barrier designs show less dc output conductance arising from the trap at the bottom interface [35]. A 5 nm channel design with graded back-barrier and Al<sub>2</sub>O<sub>3</sub> high-k gate dielectric shows improved dc performance in terms of ON-OFF ratio. This structure has the potential to scale sub-50 nm gate dimensions mantaining E-mode operation.

We have also investigated the impact of the device structure on electron mobility. The graded AlGaN barrier designs with lower 3-D Si doping in the back-barrier show higher mobility than devices with higher 3-D doping in the abrupt junction devices. Roughness scattering is found to be the dominant scattering phenomenon in the vertically scaled channel devices.

Incorporation of the strain-free lattice matched InAlN back-barrier design in E-mode technology could provide more flexibility and improvement of E-mode designs. A systematic study on the correlation between the growth method and device structure on electron mobility will be necessary to further improve the conductivity of the sidewall access regions.

#### Acknowledgment

This work was supported by the Microsystems Technlogy Office of the Defense Advanced Research Project Agency (DARPA) through the Nitride Electronics NeXt-Generation Technology (NEXT) program monitered by Dr J Albrecht. A portion of this work was performed at the Nanofabrication Facility of the University of California Santa Barbara, part of the National Nanotechnology Infrastructure Network (NNIN) funded by the National Science Foundation (NSF). The authors thank Jim Speck, S Keller, Nidhi, S Dasgupta, D Denninghoff, S Kolluri, A Carter, N Toledo for valuable discussions related to this work.

#### References

- Nakamura S, Mukai T and Senoh M 1994 Candela-class high-brightness InGaN/AlGaN double-heterostructure blue-light-emitting diodes *Appl. Phys. Lett.* 64 1687–9

- [2] Khan M A, Bhattarai A, Kuznia J N and Olson D T 1993 High electron mobility transistor based on a GaN-Al<sub>x</sub>Ga<sub>1-x</sub>N heterojunction *Appl. Phys. Lett.* 63 1214–5

- [3] Mishra U K, Parikh P and Wu Y-F 2002 AlGaN/GaN HEMTs-an overview of device operation and applications *Proc. IEEE* 90 1022–31

- [4] Wu Y-F, Kapolnek D, Ibbetson J P, Parikh P, Keller B P and Mishra U K 2001 Very-high power density AlGaN/GaN HEMTs *IEEE Trans. Electron Devices* 48 586–90

- [5] Nakasha Y et al 2010 E-Band 85-mW Oscillator and 1.3-W amplifier ICs using 0.12 μm GaN HEMTs for millimeter-wave transceivers 2010 IEEE Compound Semiconductor Integrated Circuit Symp. (CSICS) pp 1–4

- [6] Wu Y F, Moore M, Saxler A, Wisleder T, Mishra U K and Parikh P 2005 8-watt GaN HEMTs at millimeter-wave frequencies *IEEE Int. Electron Devices Meeting*, 2005. *IEDM Technical Digest.* pp 583–5

- [7] Micovic M et al 2010 W-band GaN MMIC with 842 mW output power at 88 GHz IEEE MTT-S Int. Microwave Symp. Digest (MTT) pp 237–9

- [8] Albrecht J D, Rosker M J, Wallace H B and Tsu-Hsi C 2010 THz electronics projects at DARPA: Transistors, TMICs, and amplifiers *IEEE MTT-S Int. Microwave Symp. Digest* (*MTT*) pp 1118–21

- [9] Yue Y *et al* 2012 InAlN/AlN/GaN HEMTs with regrown ohmic contacts and  $f_T$  of 370 GHz *IEEE Electron Device Lett.* **33** 988–90

- [10] Shinohara K et al 2011 Deeply-scaled self-aligned-gate GaN DH-HEMTs with ultrahigh cutoff frequency IEEE Int. Electron Devices Meeting (IEDM) pp 19.1.1–1.4

- [11] Lee D S et al 2011 Impact of GaN channel scaling in InAlN/GaN HEMTS IEEE Int. Electron Devices Meeting (IEDM) pp 19.2.1–2.4

- [12] Sun H et al 2010 205-GHz (Al,In)N/GaN HEMTs IEEE Electron Device Lett. 31 957–9

- [13] Lee D S et al 2011 245-GHz InAlN/GaN HEMTs with oxygen plasma treatment IEEE Electron Device Lett. 32 755–7

- [14] Lee D S, Xiang G, Shiping G, Kopp D, Fay P and Palacios T 2011 300-GHz InAlN/GaN HEMTs with InGaN back barrier *IEEE Electron Device Lett.* 32 1525–7

- [15] Lee D S, Xiang G, Shiping G and Palacios T 2011 InAlN/GaN HEMTs with AlGaN back barriers *IEEE Electron Device Lett.* **32** 617–9

- [16] Li G et al 2012 Ultrathin body GaN-on-insulator quantum well FETs with regrown ohmic contacts *IEEE Electron Device Lett.* 33 661–3

- [17] Rajan S, Chini A, Wong M H, Speck J S and Mishra U K 2007 N-polar GaN/AlGaN/GaN high electron mobility transistors J. Appl. Phys. 102 044501

- [18] Guerra D, Saraniti M, Faralli N, Ferry D K, Goodnick S M and Marino F A 2010 Comparison of N- and Ga-face GaN HEMTs through cellular monte carlo simulations *IEEE Trans. Electron Devices* 57 3348–54

- [19] Mishra U K et al 2010 N-polar GaN-based MIS-HEMTs for mixed signal applications IEEE MTT-S Int. Microwave Symp. Digest (MTT) p 1

- [20] Nidhi, Dasgupta S, Lu J, Speck J S and Mishra U K 2012 Scaled self-aligned N-polar GaN/AlGaN MIS-HEMTs with f<sub>T</sub> of 275 GHz IEEE Electron Device Lett. 33 961–3

- [21] Denninghoff D, Lu J, Laurent M, Ahmadi E, Keller S and Mishra U K 2012 N-polar GaN/InAlN MIS-HEMT with 400-GHz f<sub>max</sub> 70th Annual Device Research Conf. (DRC) pp 151–2

- [22] Kolluri S, Keller S, DenBaars S P and Mishra U K 2011 N-polar GaN MIS-HEMTs with a 12.1-W mm<sup>-1</sup> continuous-wave output power density at 4 GHz on sapphire substrate *IEEE Electron Device Lett.* 32 635–7

- [23] Kolluri S, Keller S, DenBaars S P and Mishra U K 2011 N-polar AlGaN/GaN MIS-HEMTs on SiC with a 16.7 W mm<sup>-1</sup> power density at 10 GHz using an Al<sub>2</sub>O<sub>3</sub> based etch stop technology for the gate recess 69th Annual Device Research Conf. (DRC) pp 215–6

- [24] Nidhi, Dasgupta S, Brown D F, Keller S, Speck J S and Mishra U K 2009 N-polar GaN-based highly scaled self-aligned MIS-HEMTs with state-of-the-art  $f_T.L_G$  product of 16.8 GHz- $\mu$ m *IEEE Int. Electron Devices Meeting* (*IEDM*) pp 1–3

- [25] Nidhi, Dasgupta S, Lu J, Wu F, Keller S, Speck J S and Mishra U K 2011 Trap-related delay analysis of self-aligned N-polar GaN/InAlN HEMTs with record extrinsic gm of 1105 mS mm<sup>-1</sup> 69th Annual Device Research Conf. (DRC) 279–80

- [26] Dasgupta S et al 2010 Ultralow nonalloyed Ohmic contact resistance to self aligned N-polar GaN high electron mobility transistors by In(Ga)N regrowth Appl. Phys. Lett. 96 143504

- [27] Singisetti U *et al* 2011 Enhancement-mode N-polar GaN MISFETs with self-aligned source/drain regrowth *IEEE Electron Device Lett.* **32** 137–9

- [28] Singisetti U et al 2010 Scalable E-mode N-polar GaN MISFET devices and process with self-aligned source/drain regrowth Device Research Conf. (DRC), 2010 pp 191–2

- [29] Singisetti U et al 2009 In<sub>0.53</sub>Ga<sub>0.47</sub>As channel MOSFETs with self-aligned InAs source/drain formed by MEE regrowth IEEE Electron Device Lett. 30 1128–30

- [30] Higashiwaki M et al 2009 A comparative study of effects of SiN<sub>x</sub> deposition method on AlGaN/GaN heterostructure field-effect transistors Appl. Phys. Lett. 94 053513

- [31] Higashiwaki M, Mimura T and Matsui T 2007 Enhancement-mode AlN/GaN HFETs using Cat-CVD SiN IEEE Trans. Electron Devices 54 1566–70

- [32] Ide T et al Gate-length dependence of DC characteristics in submicron-gate AlGaN/GaN high electron mobility transistors Japan. J. Appl. Phys. 46 2334

- [33] Jessen G H et al 2007 Short-channel effect limitations on high-frequency operation of AlGaN/GaN HEMTs for T-gate devices Electron Devices IEEE Trans.

54 2589–97

- [34] Wong M H, Singisetti U, Lu J, Speck J S and Mishra U K 2011 Anomalous output conductance in N-polar GaN-based MIS-HEMTs 69th Annual Device Research Conf. (DRC) pp 211–2

- [35] Wong M H, Singisetti U, Lu J, Speck J S and Mishra U K 2012 Anomalous output conductance in N-polar GaN high electron mobility transistors *IEEE Trans. Electron Devices* 59 2988–95

- [36] Liu Z H et al 1993 Threshold voltage model for deep-submicrometer MOSFETs IEEE Trans. Electron Devices 40 86–95

- [37] Jia G et al 2012 MBE-regrown ohmics in InAlN HEMTs with a regrowth interface resistance of 0.05Ωmm IEEE Electron Device Lett. 33 525–7

- [38] Singisetti U, Wong M H, Dasgupta S, Speck J S and Mishra U K Enhancement-mode N-polar GaN metal-insulator-semiconductor field effect transistors with current gain cutoff frequency of 120 GHz Appl. Phys. Express 4 024103

- [39] Koolen M C A M, Geelen J A M and Versleijen M P J G 1991 An improved de-embedding technique for on-wafer high-frequency characterization *Proc. Bipolar Circuits and Technology Meeting* pp 188–91

- [40] Wang X High-electron-mobility InN layers grown by boundary-temperature-controlled epitaxy Appl. Phys. Express 5 015502

- [41] Lundstrom M S *et al* 2001 On the mobility versus drain current relation for a nanoscale MOSFET *Electron Device Lett. IEEE* 22 293–5

- [42] Singisetti U, Wong M H and Mishra U K 2012 Interface roughness scattering in ultra-thin N-polar GaN quantum well channels *Appl. Phys. Lett.* **101** 012101

- [43] Nidhi, Rajan S, Keller S, Wu F, DenBaars S P, Speck J S and Mishra U K 2008 Study of interface barrier of SiN<sub>x</sub>/GaN interface for nitrogen-polar GaN based high electron mobility transistors J. Appl. Phys. 103 124508

- [44] Sakaki H, Noda T, Hirakawa K, Tanaka M and Matsusue T 1987 Interface roughness scattering in GaAs/AlAs quantum wells Appl. Phys. Lett. 51 1934–6

- [45] Jana R K and Jena D 2011 Stark-effect scattering in rough quantum wells Appl. Phys. Lett. 99 012104

- [46] Ahn D and Chuang S L 1986 Variational calculations of subbands in a quantum well with uniform electric field: Gram–schmidt orthogonalization approach *Appl. Phys. Lett.* 49 1450–2

- [47] Miller D A B et al 1985 Electric field dependence of optical absorption near the band gap of quantum-well structures *Phys. Rev.* B 32 1043–60

- [48] Price P J 1981 Two-dimensional electron transport in semiconductor layers: II. Screening J. Vac. Sci. Technol. 19 599–603

- [49] Cao Y and Jena D 2007 High-mobility window for two-dimensional electron gases at ultrathin AlN/GaN heterojunctions Appl. Phys. Lett. 90

- [50] Ando T, Fowler A B and Stern F 1982 Electronic properties of two-dimensional systems *Rev. Mod. Phys.* 54 437–672

- [51] Singisetti U, Wong M H, Speck J S and Mishra U K 2012 Enhancement-mode N-polar GaN MOS-HFET with 5-nm GaN channel, 510-mS mm<sup>-1</sup> g(m), and 0.66-omega. mm R(on) IEEE Electron Device Lett. 33 26–8

- [52] Shinohara K et al 2010 220 GHz f<sub>r</sub> and 400 GHz f<sub>max</sub> in 40-nm GaN DH-HEMTs with re-grown ohmic IEEE Int. Electron Devices Meeting (IEDM) pp 30.1.1–1.4