## Scaling of electroresistance effect in fully integrated ferroelectric tunnel junctions

Mohammad Abuwasib, Haidong Lu, Tao Li, Pratyush Buragohain, Hyungwoo Lee, Chang-Beom Eom, Alexei Gruverman, and Uttam Singisetti

Citation: Applied Physics Letters 108, 152904 (2016); doi: 10.1063/1.4947020

View online: http://dx.doi.org/10.1063/1.4947020

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/108/15?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Temperature-dependent tunneling electroresistance in Pt/BaTiO3/SrRuO3 ferroelectric tunnel junctions Appl. Phys. Lett. **103**, 132913 (2013); 10.1063/1.4823580

Interfacial dead layer effects on current-voltage characteristics in asymmetric ferroelectric tunnel junctions J. Appl. Phys. **113**, 174101 (2013); 10.1063/1.4803151

First-principles calculations of size-dependent giant electroresistance effect in nanoscale asymmetric ferroelectric tunnel junctions

J. Appl. Phys. 111, 074102 (2012); 10.1063/1.3698503

Coexistence of tunneling magnetoresistance and electroresistance at room temperature in La0.7Sr0.3MnO3/(Ba, Sr)TiO3/La0.7Sr0.3MnO3 multiferroic tunnel junctions

J. Appl. Phys. 109, 07D915 (2011); 10.1063/1.3564970

Effects of electrodes and space charges on the tunneling electroresistance in the ferroelectric tunnel junction with a SrTiO 3 / BaTiO 3 composite barrier

Appl. Phys. Lett. 96, 252905 (2010); 10.1063/1.3457451

## Scaling of electroresistance effect in fully integrated ferroelectric tunnel junctions

Mohammad Abuwasib, <sup>1</sup> Haidong Lu, <sup>2</sup> Tao Li, <sup>2</sup> Pratyush Buragohain, <sup>2</sup> Hyungwoo Lee, <sup>3</sup> Chang-Beom Eom, <sup>3</sup> Alexei Gruverman, <sup>2</sup> and Uttam Singisetti <sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, University at Buffalo, Buffalo, New York 14260, USA

Wisconsin 53706, USA

(Received 11 December 2015; accepted 30 March 2016; published online 13 April 2016)

Systematic investigation of the scalability for tunneling electroresistance (TER) of integrated Co/BaTiO<sub>3</sub>/SrRuO<sub>3</sub> ferroelectric tunnel junctions (FTJs) has been performed from micron to deep submicron dimensions. Pulsed measurements of the transient currents confirm the ferroelectric switching behavior of the FTJs, while the hysteresis loops measured by means of piezoresponse force microscopy verify the scalability of these structures. Fully integrated functional FTJ devices with the size of  $300 \times 300 \,\mathrm{nm}^2$  exhibiting a tunneling electroresistance (TER) effect of the order of  $2.7 \times 10^4\%$  have been fabricated and tested. Measured current density of  $75 \,\mathrm{A/cm}^2$  for the ON state and a long polarization retention time of ON state (>10 h) show a lot of promise for implementation of high-density BaTiO<sub>3</sub>-based FTJ memory devices in future. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4947020]

As the current trend of dimensional scaling of CMOS devices is going to reach its fundamental limit in near future, emerging beyond-CMOS technologies are extensively investigated. 1-3 Ferroelectric tunnel junctions (FTJs) are among such emerging devices that can be a potential replacement of CMOS-based traditional random access memory (RAM) in future.<sup>4–8</sup> While continuous scaling of CMOS memory beyond the 15 nm technology node faces serious speed and power challenges, 1,3 FTJ devices can be scaled down to the sub-micrometer range (<100 nm) without yielding their functional characteristics. 1,6 The advantages of the FTJ-based non-volatile memory devices as compared to other existing counterparts are non-destructive readout, 9-11 ultra-low power operation in read cycles, 4,5,7 and high read current densities leading to high-density data storage.6,9

The basic device structure of a FTJ consists of a thin (several nanometers or less) ferroelectric (FE) barrier separating two electrodes. Modulation of the tunnel transmission coefficient by the reversal of the polarization state of the FE layer leads to high and low resistance states and large tunneling electroresistance (TER). A choice of the two electrodes with dissimilar workfunctions and different screening lengths is required for the sizeable TER to occur. Various FTJs employing different FE barriers and electrode materials have been experimentally demonstrated using conducting atomic force microscopy/piezoresponse force microscopy (c-AFM/PFM) measurements. 7,9–11,13–15

The choice of electrodes and ferroelectric barrier materials is important for optimization of the FTJs performance as well as for CMOS compatibility of the FTJs fabrication process. For example, it was recently reported that the use of La<sub>0.67</sub>Sr<sub>0.33</sub>MnO<sub>3</sub> (LSMO) layer as the bottom electrode in FTJs has serious technological challenges in integration due to the degradation of the LSMO conductivity<sup>16</sup> after

exposure to chlorine plasma based reactive ion etch (RIE) process. In contrast, SrRuO<sub>3</sub> (SRO) was recently demonstrated to be stable under semiconductor fabrication process steps. <sup>17,18</sup> Cobalt (Co) is an attractive choice for the top electrode as it can stabilize the ferroelectric polarization and hence give long retention. <sup>19,20</sup> The scalability of ferroelectricity in BaTiO<sub>3</sub> (BTO) films down to ~1 nm (Ref. 21) by strain engineering makes it an attractive choice as a FE tunnel barrier. BTO/SRO-based FTJs with Pt top electrode has been reported which was characterized by conducting AFM (c-AFM)/PFM techniques. <sup>10,22,23</sup> However, the functionality of BTO/SRO heterostructure with Co top electrode has not been investigated yet.

FTJ device characteristics can be evaluated using PFM/ c-AFM measurements; however, a fully integrated FTJ device with standard Si device test structures is necessary to investigate advanced switching dynamics, fast pulse measurements, high frequency characteristics, and reliability. In addition, the scalability, the parasitic resistance and capacitances, and integration challenges with Si need to be evaluated in an integrated FTJ device. Recently, the size dependence of polarization switching and tunnel electro resistance (TER) in a Ru/BTO/LSMO heterostructure was demonstrated by PFM characterization.<sup>24</sup> A fully integrated FTJ device with Co/BiFeO<sub>3</sub>(BFO)/Ca<sub>0.96</sub>Ce<sub>0.04</sub>MnO<sub>3</sub> (CCMO) layers was also recently reported with sub-micron devices.<sup>25</sup> However, the switching dynamics and scalability of Co/BTO/SRO FTJ heterostructure has not been investigated. In this letter, we report fully integrated Co/BTO/SRO FTJs of size  $\sim 300 \times 300 \,\mathrm{nm}^2$ . The ferroelectric properties of the ultrathin BTO films in the FTJ heterostructure were verified by Positive Up Negative Down (PUND) test. Additionally, systematic verification of ferroelectricity and scalability of the Co/BTO/SRO heterostructure was confirmed down to  $200 \times 200 \,\mathrm{nm}^2$  using PFM measurements.

<sup>&</sup>lt;sup>2</sup>Departments of Physics and Astronomy, University of Nebraska-Lincoln, Lincoln, Nebraska 68588, USA <sup>3</sup>Department of Materials Science and Engineering, University of Wisconsin-Madison, Madison,

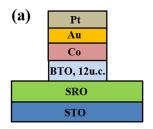

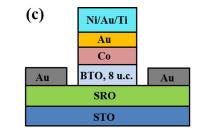

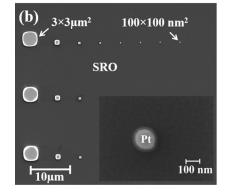

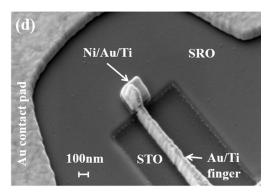

FIG. 1. (a) Cross-section schematic of the Co/BTO(12 u.c.)/SRO FTJ used in PFM/AFM study, (b) Scanning electron micrograph of FTJs with Pt top electrode scaled down in sizes from  $3\times3~\mu\mathrm{m}^2$  (leftmost) to  $100\times100~\mathrm{nm}^2$  (rightmost). Inset: A  $100\times100~\mathrm{nm}^2$  FTJs with 40 nm thick Pt electrode used for PFM measurements. (c) Cross-section schematic of Co/BTO(8 u.c.)/SRO integrated FTJ and (d) SEM image of a  $300\times300~\mathrm{nm}^2$  integrated FTJ device.

The BTO (8 u.c., 12 u.c.)/SRO (40 nm) heterostructures were grown epitaxially on atomically smooth TiO2-terminated (001)-SrTiO<sub>3</sub> (STO) substrates using pulsed laser deposition (PLD). For the TiO<sub>2</sub> termination, low angle miscut (<0.1°) SrTiO<sub>3</sub> substrates were etched using buffered HF acid for 60 s and then were annealed in oxygen at 1000 °C for 6 h. The SRO and BTO thin films were grown at 680 °C with chamber oxygen pressure kept at 0.12 mbar. After the growth, the samples were cooled down to room temperature in oxygen atmosphere at  $\sim$ 1000 mbar in order to minimize the amount of oxygen vacancy in the thin films. 19,21 A blanket 5 nm thick Co is deposited on BTO followed by 10 nm gold (Au) as a cap layer using sputtered deposition. Further details of growth and characterization can be found elsewhere. 10,17,21 To check the scalability of the ferroelectric properties by PFM measurements, 12 u.c. BTO films were used whereas 8 u.c. BTO films were used for integrated devices. Square-shaped FTJ structures with varying sizes from  $3 \times 3 \,\mu\text{m}^2$  to  $200 \times 200 \,\text{nm}^2$  were fabricated in the following way. First, 40-nm-thick Pt electrodes were patterned by electron beam lithography (EBL). Pt films were used as they are resistant to oxidation, which is detrimental for PFM measurements. Next, the Au(10 nm)/Co(5 nm)/BTO(12 u.c.)layers were etched using BCl<sub>3</sub>/Ar based RIE plasma with the Pt as the etch mask. A cross-section of the resulting device structure and the SEM micrograph of the fabricated FTJs are shown in Figs. 1(a) and 1(b), respectively. For the integrated sub-micron FTJ devices, a Ni (50 nm)/Au (90 nm)/Ti (20 nm) layer was first deposited by electron beam evaporation after patterning by EBL. The Au (10 nm)/Co (5 nm)/ BTO (8 u.c.) layers were then etched in BCl<sub>3</sub>/Ar based RIE using Ni as the etch mask. <sup>16</sup> Next,  $80 \times 40 \,\mu\text{m}^2$  Au contact pads were defined on SRO. After ion milling of the conducting SRO films ( $\sim$ 40 nm),  $80 \times 40 \,\mu\text{m}^2$  Au (150 nm)/Ti (20 nm) contact pads were defined on the insulating STO substrate. Finally, the contact finger of Au(150 nm)/ Ti(20 nm) was deposited by electron beam deposition to connect the contact pad on STO substrate to the top of Ni/Au/Ti

layer. The poor step coverage of the electron beam deposition ensures there is no short between the contact finger and the SRO sidewall.<sup>26</sup> The cross-section and the SEM micrograph of the integrated  $300 \times 300 \,\mathrm{nm}^2$  FTJ device are shown in Figs. 1(c) and 1(d), respectively.

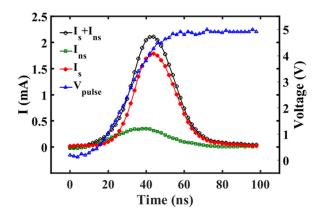

The ferroelectric properties of the ultrathin BTO films were first verified by the standard PUND (Positive Up Negative Down) method, which relies on the measurement of the switching currents ( $I_s$ ) for decisive identification of the presence of the polarization charge. PUND measurements were carried out for a 10- $\mu$ m-diameter Au/Co/BTO(12 u.c.)/SRO/STO FTJs grown under similar conditions (Fig. 2). The details of the PUND measurement setup can be found elsewhere. Polarization switching current ( $I_s$ ) was detected (Fig. 2) from the difference between the total transient current that includes both the polarization switching and non-switching (capacitive charging) current components ( $I_s + I_{ns}$ ) and the non-switching current ( $I_{ns}$ ). Integration of this differential signal yielded the polarization value of about  $31.5 \, \mu$ C/cm<sup>2</sup>, which is consistent with the

FIG. 2. PUND (Positive Up Negative Down) testing of 10- $\mu$ m-diameter Co/BTO(12 u.c.)/SRO/STO FTJs. The switching current ( $I_s$ ) was measured from the difference of the total transient current ( $I_s+I_{ns}$ ) and the non-switching current ( $I_{ns}$ ). The measured switchable polarization is about 31.5  $\mu$ C/cm<sup>2</sup> consistent with polarization value of bulk BTO.

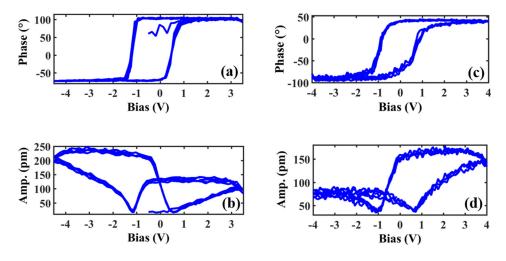

FIG. 3. PFM (a) phase and (b) amplitude loop for the  $3\times3\,\mu\text{m}^2$  Co/BTO(12 u.c.)/SRO FTJ, and the (c) phase and (d) amplitude loop for the  $200\times200\,\text{nm}^2$  Co/BTO(12 u.c.)/SRO FTJ measured in off-field (DC-bias off) regime.

polarization value of bulk BTO thus confirming the ferroelectric properties of ultrathin BTO film in the FTJ heterostructure.

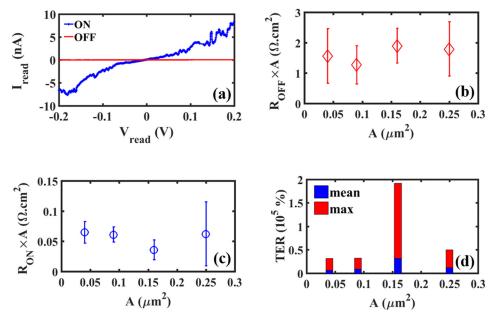

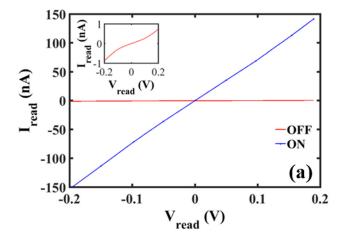

The PFM and c-AFM measurements of the Pt/Au/Co/ BTO/SRO devices were performed using an Asylum MFP-3D atomic force microscope (AFM). Figure 3 shows the PFM phase and amplitude hysteresis loops for  $3 \times 3 \mu m^2$  and  $200 \times 200 \,\mathrm{nm}^2$  FTJs, measured in the off-field (DC bias off) regime. Ferroelectric polarization switching was observed for all the devices at the coercive voltage ( $V_c \sim \pm 1 \text{ V}$ ) confirming the scalability of this FTJ structure down to nanoscale dimensions.  $^{7,10,19,23,24}$  In the smaller  $200 \times 200 \text{ nm}^2$ FTJs, the PFM amplitude was slightly lower than in the larger  $3 \times 3 \,\mu\text{m}^2$  FTJs, which can be partially attributed to the processing damage around the top electrode perimeter. The smallest FTJ of  $200 \times 200 \,\mathrm{nm}^2$  area exhibits a significant PFM signal, which indicates a good scalability of these devices in terms of maintaining their ferroelectric properties even after fabrication steps. The observed left shift of the PFM hysteresis loop in the range of -0.25 V to -0.5 V may be attributed to the built-in electric field resulting from the different top and bottom interfaces as well as due to the different ON and OFF resistance states.30-32 The I-V measurements were performed with the write and read voltage pulses of  $\pm 3 \,\mathrm{V}$  and  $\pm 0.2 \,\mathrm{V}$ , respectively, with  $100 \,\mathrm{ms}$ poling time. The current compliance was set at 20 nA to prevent any local joule heating or electroforming in FTJs.<sup>33</sup> I-V curve during read operation obtained in a  $200 \times 200 \,\mathrm{nm}^2$  FTJ is shown in Fig. 4(a). Several FTJs were measured for each area (A) to see the scaling effects down to nanoscale. Resistance-area products  $(R \times A)$  in the OFF and ON states, and %TER, are plotted in Figs. 4(b)-4(d), respectively. The nearly constant  $R_{ON} \times A$  product with a mean of  $\sim 0.05~\Omega$ cm<sup>2</sup> for different areas FTJ matches with the reported value<sup>34</sup> verifying the ferroelectric switching at nanoscale.<sup>33</sup> The average %TER is  $1.5 \times 10^4$ % among the measured devices with a maximum observed TER is  $1.6 \times 10^5\%$  for a  $400 \times 400 \,\mathrm{nm}^2$  FTJ. The switching cycle measurement shows an endurance of  $\sim$ 20, after that OFF/ON resistance ratio becomes  $\sim 1$ .

I-V measurements of the integrated FTJs were performed using HP4155B parameter analyzer and JR2745 microwave probe station. The write voltage was  $\pm 3$  V with 100 ms poling and read voltage was  $\pm 0.2$  V. Current compliance was set at 1  $\mu$ A during the write pulse to prevent any local joule heating or filament formation by large current

FIG. 4. FTJs with Co/BTO(12 u.c.)/SRO heterostructure measured by c-AFM (a) I-V curve during read operation (I<sub>read</sub> vs. V<sub>read</sub>). Resistance-area product with respect to the FTJ area (A) for (b) OFF state (R<sub>OFF</sub> × A) and (c) ON state (R<sub>ON</sub> × A). The write voltage (V<sub>write</sub>) and read voltage (V<sub>read</sub>) were  $\pm 3$  V and  $\pm 0.2$  V, respectively, for resistance calculation. (d) Mean (blue) and maximum (red) tunneling electroresistance (%TER) with area (A) of the FTJs.

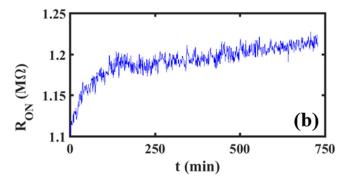

FIG. 5. (a) I-V curves for the  $300\times300\,\mathrm{nm}^2$  integrated Co/BTO(8 u.c.)/SRO FTJ devices in ON and OFF resistance states, corresponding to the opposite polarizations. The applied write voltages were  $\pm3\,\mathrm{V}$  with a poling time of 100 ms. Inset: Enlarged view of the I-V curve for the OFF resistance state. (b) The ON resistance ( $R_{\mathrm{ON}}$ ) as a function of time (t) for a  $300\times300\,\mathrm{nm}^2$  integrated FTJ.  $R_{\mathrm{ON}}$  was measured after 1 min interval up to 12 h at a read voltage of  $V_{\mathrm{read}}=0.2\,\mathrm{V}$ .

flow during write operation.<sup>33</sup> Figure 5(a) shows the I-V characteristics in the ON and OFF state of the  $300 \times 300 \text{ nm}^2$ integrated FTJ during the read operation. Almost linear tunnel current was observed in the ON state for small bias voltage.  $^{10,35-37}$  The ON and OFF state resistances are  $R_{\rm ON}\sim 1.4$  $M\Omega$  and  $R_{OFF} \sim 370$   $M\Omega$ , respectively, giving TER of  $\sim 2.7 \times 10^4$ %. The ON current density at the read voltage of 0.1 V was observed to be high 75 A/cm<sup>2</sup>, which is larger than the previously reported values (~10 A/cm<sup>2</sup>).<sup>38,39</sup> Large ON current density is attractive for further scaling the FTJs down to sub-50 nm dimensions without losing reliable resistive readout which is promising for high density memory implementation. Figure 5(b) shows the measured ON resistance (R<sub>ON</sub>) with time (t) up to 12 h. Initial ON resistance  $(R_{ON} = 1.1 \text{ M}\Omega)$  increases slightly by 10% after 12 h, which shows stable ferroelectric polarization retention in nanometer sized integrated FTJ. However, the switching endurance in the integrated device was also observed to be low  $\sim$ 25 similar to what was observed in PFM measurements due to the interfacial effects such as interface termination in ultrathin SRO/STO film which causes such poor endurance and unstable polarization. 40 Switching endurance can be improved by interface engineering, the optimization of the growth conditions, the thickness of the top metal electrode, and incorporating additional interface layers in the junctions<sup>40</sup> which will be investigated separately in future.

In conclusion, we demonstrate the ferroelectric properties of ultrathin BTO in a Co/BTO/SRO FTJ heterostructure by PUND measurements. The scalability of Co/BTO/SRO FTJs to nanoscale ( $\sim\!200\times200\,\mathrm{nm}^2$ ) dimensions was verified by PFM measurements. We also report fully integrated functional submicron FTJs with large TER of  $\sim\!2.7\times10^4\%$  and long ferroelectric polarization retention. A  $300\times300\,\mathrm{nm}^2$  fully integrated FTJ shows large read current density (75 A/cm²) which is promising for further scaling of Co/BTO/SRO based FTJs for ultra-low power non-volatile memory applications.

This project was supported by the Semiconductor Research Corporation (SRC) through the Center for Nanoferroic Devices (CNFD), an SRC-NRI Nanoelectronics Research Initiative Center under Task ID 2398.002. A part of this research was performed in the University at Buffalo Electrical Engineering Cleanroom and the Materials Characterization Laboratory, part of the university's Shared Instrumentation Laboratories.

<sup>1</sup>J. A. Hutchby, R. Cavin, V. Zhirnov, J. E. Brewer, and G. Bourianoff, Computer **41**(5), 28–32 (2008).

<sup>2</sup>A. Chen, J. Hutchby, V. Zhirnov, and G. Bourianoff, *Emerging Nanoelectronic Devices* (John Wiley and Sons, 2014).

<sup>3</sup>ITRS Roadmap, see http://www.itrs.net/Links/2011ITRS/2011Chapters/ 2011ExecSum.pdf for Semiconductor Industry Association (2011).

<sup>4</sup>E. Y. Tsymbal and A. Gruverman, Nat. Mater. 12(7), 602–604 (2013).

<sup>5</sup>A. M. Ionescu, Nat. Nanotechnol. **7**(2), 83–85 (2012).

<sup>6</sup>V. Garcia and M. Bibes, Nat. Commun. 5, 4289 (2014).

<sup>7</sup>A. Chanthbouala, A. Crassous, V. Garcia, K. Bouzehouane, S. Fusil, X. Moya, J. Allibe, B. Dlubak, J. Grollier, S. Xavier, C. Deranlot, A. Moshar, R. Proksch, N. D. Mathur, M. Bibes, and A. Barthelemy, Nat. Nanotechnol. 7(2), 101–104 (2012).

<sup>8</sup>E. Y. Tsymbal, A. Gruverman, V. Garcia, M. Bibes, and A. Barthélémy, MRS Bull. 37(02), 138–143 (2012).

<sup>9</sup>V. Garcia, S. Fusil, K. Bouzehouane, S. Enouz-Vedrenne, N. D. Mathur, A. Barthelemy, and M. Bibes, Nature 460(7251), 81–84 (2009).

<sup>10</sup>A. Gruverman, D. Wu, H. Lu, Y. Wang, H. W. Jang, C. M. Folkman, M. Y. Zhuravlev, D. Felker, M. Rzchowski, C. B. Eom, and E. Y. Tsymbal, Nano Lett. 9(10), 3539–3543 (2009).

<sup>11</sup>Z. Wen, C. Li, D. Wu, A. Li, and N. Ming, Nat. Mater. **12**(7), 617–621 (2013).

<sup>12</sup>M. Y. Zhuravlev, R. F. Sabirianov, S. S. Jaswal, and E. Y. Tsymbal, Phys. Rev. Lett. **94**(24), 246802 (2005).

<sup>13</sup>H. Yamada, V. Garcia, S. Fusil, S. Boyn, M. Marinova, A. Gloter, S. Xavier, J. Grollier, E. Jacquet, C. Carrétéro, C. Deranlot, M. Bibes, and A. Barthélémy, ACS Nano 7(6), 5385–5390 (2013).

<sup>14</sup>P. Maksymovych, S. Jesse, P. Yu, R. Ramesh, A. P. Baddorf, and S. V. Kalinin, Science 324(5933), 1421–1425 (2009).

<sup>15</sup>R. Guo, Z. Wang, S. Zeng, K. Han, L. Huang, D. G. Schlom, T. Venkatesan, Ariando, and J. Chen, Sci. Rep. 5, 12576 (2015).

<sup>16</sup>M. Abuwasib, L. Hyungwoo, P. Sharma, E. Chang-Beom, A. Gruverman, and U. Singisetti, in 73rd Annual Device Research Conference (DRC) (2015), pp. 45–46.

<sup>17</sup>C. Eom, R. Cava, R. Fleming, J. M. Phillips, J. Marshall, J. Hsu, J. Krajewski, and W. Peck, Science 258(5089), 1766–1769 (1992).

<sup>18</sup>M. Abuwasib, H. Lee, C.-B. Eom, A. Gruverman, and U. Singisetti, Appl. Phys. Lett. **107**(24), 242905 (2015).

<sup>19</sup>D. J. Kim, H. Lu, S. Ryu, C. W. Bark, C. B. Eom, E. Y. Tsymbal, and A. Gruverman, Nano Lett. **12**(11), 5697–5702 (2012).

<sup>20</sup>A. Chanthbouala, V. Garcia, R. O. Cherifi, K. Bouzehouane, S. Fusil, X. Moya, S. Xavier, H. Yamada, C. Deranlot, N. D. Mathur, M. Bibes, A. Barthélémy, and J. Grollier, Nat. Mater. 11(10), 860–864 (2012).

<sup>21</sup>K. J. Choi, M. Biegalski, Y. L. Li, A. Sharan, J. Schubert, R. Uecker, P. Reiche, Y. B. Chen, X. Q. Pan, V. Gopalan, L.-Q. Chen, D. G. Schlom, and C. B. Eom, Science 306(5698), 1005–1009 (2004).

<sup>22</sup>Z. Wen, L. You, J. Wang, A. Li, and D. Wu, Appl. Phys. Lett. **103**(13), 132913 (2013).

<sup>23</sup>A. Sokolov, O. Bak, H. Lu, S. Li, E. Y. Tsymbal, and A. Gruverman, Nanotechnology 26(30), 305202 (2015).

- <sup>24</sup>A. V. Singh, M. Althammer, K. Rott, G. Reiss, and A. Gupta, Appl. Phys. Lett. **107**(12), 122903 (2015).

- <sup>25</sup>S. Boyn, S. Girod, V. Garcia, S. Fusil, S. Xavier, C. Deranlot, H. Yamada, C. Carrétéro, E. Jacquet, M. Bibes, A. Barthélémy, and J. Grollier, Appl. Phys. Lett. 104(5), 052909 (2014).

- <sup>26</sup>J. D. Plummer, Silicon VLSI technology: Fundamentals, practice, and Modeling (Pearson Education India, 2009).

- <sup>27</sup>C. Dehoff, B. J. Rodriguez, A. I. Kingon, R. J. Nemanich, A. Gruverman, and J. S. Cross, Rev. Sci. Instrum. 76(2), 023708 (2005).

- <sup>28</sup>A. Stamm, D. J. Kim, H. Lu, C. W. Bark, C. B. Eom, and A. Gruverman, Appl. Phys. Lett. **102**(9), 092901 (2013).

- <sup>29</sup>J. F. Scott, L. Kammerdiner, M. Parris, S. Traynor, V. Ottenbacher, A. Shawabkeh, and W. F. Oliver, J. Appl. Phys. 64(2), 787–792 (1988).

- <sup>30</sup>A. Gruverman, A. Kholkin, A. Kingon, and H. Tokumoto, Appl. Phys. Lett. **78**(18), 2751–2753 (2001).

- <sup>31</sup>J. Chen, Y. Luo, X. Ou, G. Yuan, Y. Wang, Y. Yang, J. Yin, and Z. Liu, J. Appl. Phys. 113(20), 204105 (2013).

- <sup>32</sup>Y. Luo, X. Li, L. Chang, W. Gao, G. Yuan, J. Yin, and Z. Liu, AIP Adv. 3(12), 122101 (2013).

- <sup>33</sup>H. Kohlstedt, A. Petraru, K. Szot, A. Rüdiger, P. Meuffels, H. Haselier, R. Waser, and V. Nagarajan, Appl. Phys. Lett. 92(6), 062907 (2008).

- <sup>34</sup>C. Li, L. Huang, T. Li, W. Lü, X. Qiu, Z. Huang, Z. Liu, S. Zeng, R. Guo, Y. Zhao, K. Zeng, M. Coey, J. Chen, Ariando, and T. Venkatesan, Nano Lett. 15(4), 2568–2573 (2015).

- <sup>35</sup>J. G. Simmons, J. Appl. Phys. **34**(6), 1793–1803 (1963).

- <sup>36</sup>J. C. Fisher and I. Giaever, J. Appl. Phys. **32**(2), 172–177 (1961).

- <sup>37</sup>J. G. Simmons, G. J. Unterkofler, and W. W. Allen, Appl. Phys. Lett. 2(4), 78–80 (1963).

- <sup>38</sup>D. Pantel, S. Goetze, D. Hesse, and M. Alexe, ACS Nano 5(7), 6032–6038 (2011).

- <sup>39</sup>A. Q. Jiang, C. Wang, K. J. Jin, X. B. Liu, J. F. Scott, C. S. Hwang, T. A. Tang, H. B. Lu, and G. Z. Yang, Adv. Mater. 23(10), 1277–1281 (2011).

- <sup>40</sup>H. Lu, X. Liu, J. Burton, C. W. Bark, Y. Wang, Y. Zhang, D. Kim, A. Stamm, P. Lukashev, and D. Felker, Adv. Mater. 24(9), 1209–1216 (2012).