## inGaAs channel MOSFET with self-aligned source/drain MBE regrowth technology

Uttam Singisetti<sup>\*1</sup>, Mark A. Wistey<sup>1,2</sup>, Gregory J. Burek<sup>1</sup>, Erdem Arkun<sup>2</sup>, Ashish K. Baraskar<sup>1</sup>, Yanning Sun<sup>3</sup>, Edward W. Kiewra<sup>3</sup>, Brian J. Thibeault<sup>1</sup>, Arthur C. Gossard<sup>1,2</sup>, Chris J. Palmstrøm<sup>1,2</sup>, and Mark J. W. Rodwell<sup>1</sup>

Received 13 September 2008, accepted 2 January 2009 Published online 20 April 2009

PACS 73.40.Kp, 81.05.Ea, 81.15.Hi, 85.30.Tv

InGaAs is a promising alternative channel material to Si for sub-22 nm node technology because of its low electron effective mass ( $m^*$ ) hence high electron velocities. We report a gate-first MOSFET process with self-aligned source/drain formation using non-selective MBE re-growth, suitable for realizing high performance scaled III-V MOSFETs. A W/Cr/SiO<sub>2</sub> gate stack was defined on thin (4 nm/2.5 nm) In-GaAs/InP channel by an alternating selective dry etch technique. A 5 nm  $Al_2O_3$  layer was used as gate dielectric. An InAlAs bottom barrier provided vertical confinement of the channel. An *in-situ* H cleaning of the wafer leaves an epiready surface suitable for MBE or MOCVD regrowth.

Source/Drain region were defined by non-selective MBE regrowth and *in situ* molybdenum contacts. First generation of devices fabricated using this process showed extremely low drive current of 2  $\mu A/\mu m$ . The drive current was limited by an extremely high source resistance. A regrowth gap between source/drain and gate was the cause for high source resistance. The gap in the regrowth was because of low growth temperature (400 °C). A modified high temperature growth technique resolved the problem.

© 2009 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim

Si is expected to reach the scaling limit beyond 22 nm gate node mainly due to the inability to achieve low leakage sub-0.5 nm equivalent oxide thickness (EOT) gate dielectrics. Also, sub-22 nm gate length and sub-1 nm EOT Si devices cannot realize complete ballistic transport, hence not achieving the full potential drive currents [1].

High electron velocity III-V materials are investigated as an alternative channel to Si in N-MOSFETs.  $In_xGa_{1-x}As$  ( $x \ge 0.53$ ) is a leading candidate as a channel material because of its low electron effective mass ( $m^*$ ) and high saturation velocities (v). Also the large inter-valley separation in  $In_{0.53}Ga_{0.47}As$  (InGaAs) reduces inter-valley scattering,

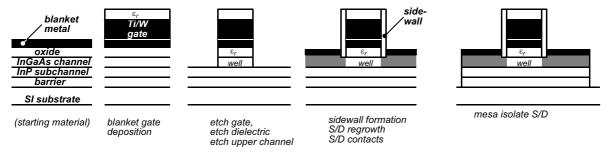

Figure 1 Overall process flow.

<sup>&</sup>lt;sup>1</sup> ECE University of California, Santa Barbara, CA, USA

<sup>&</sup>lt;sup>2</sup> Materials Departments, University of California, Santa Barbara, CA, USA

<sup>&</sup>lt;sup>3</sup> IBM T.J. Watson Research Center, Yorktown Heights, NY, USA

<sup>\*</sup> Corresponding author: e-mail uttam@ece.ucsb.edu, Phone: +18058933273, Fax: +18058933262

so electron velocities remain high even at high electric fields. The main obstacle of unpinned interfaces to high-k dielectric on InGaAs have been addressed by several groups with various high-k dielectrics [2-4]. However these devices either have long gate lengths or were not scaled vertically. The full potential of InGaAs channel devices can only be realized in MOSFETs which are scaled both horizontally and vertically.

We report the design and process flow development of a self-aligned InGaAs MOSFET using MBE regrown source/drain (S/D) regions. Detailed MOSFET scaling laws and sub-22 nm III-V FET design are discussed in references [1, 5, 6]. Lateral scaling of the gate length to 22 nm dictates a vertical scaling of the device. At sub-22 nm gate lengths, a maximum of 1 nm EOT dielectric and 5 nm thick channel with strong vertical confinement are required for maximum transconductance  $(g_m)$  and acceptably low drain induced barrier lowering (DIBL). We use In<sub>0.52</sub>Al<sub>0.48</sub>As (InAlAs) heterojunction barrier to achieve this confinement. An alternative approach using electrostatic confinement would need high  $p^+$  doping in the InGaAs channel, which would reduce the channel mobility because of impurity scattering and will also degrade the short channel effects due to discrete dopant fluctuations. In sub-22 nm devices, the device parasitic capacitances dominate and limit the circuit delay [1, 5]. The IC delay  $(\tau)$ can be reduced only through high drive current  $(I_d)$ and high  $g_m$ . InGaAs MOSFETs are expected to achieve very high drive currents (5 mA/μm) and transconductances (7 mS/ $\mu$ m) because of high thermal velocities (J = qnv) [1, 5, 6]. These current levels are achieved at a sheet concentration of  $\sim 10^{13}$  cm<sup>-2</sup>. Large intervalley separation  $(E_{\Gamma-L},\ E_{\Gamma-X}=0.5\ eV)$  in InGaAs makes it possible to achieve these densities without populating the slower satellite valleys.

Furthermore, source access resistance plays an important role in scaled devices because it degrades the available  $I_d$  and  $g_m$  from the device. Even a very low source access resistance of 15  $\Omega$ - $\mu$ m would degrade  $I_d$  by 10% [5]. This value is an order of magnitude smaller than the ITRS roadmap listed source access resistance of 180  $\Omega$ - $\mu$ m [7]. IC layout density requirement would constrain  $L_c = L_g = 22$ nm, which means a specific contact resistivity  $\rho_c = 0.25 \Omega$ - $\mu \text{m}^2$  corresponding to 10  $\Omega$ - $\mu \text{m}$  resistance. A 4  $\Omega$ - $\mu \text{m}$  S/D extension access resistance translates into a high 5×1019 cm<sup>-3</sup> active doping in these regions. Besides source resistance, high doping concentrations is required in S/D to avoid "source starvation" [6]. Unlike Si, ion implantation is not a viable technique for InGaAs due to various difficulties. There is no data showing the capability of implantation realizing these high active concentrations and contact resistance values. Instead we are using MBE to regrow S/D regions after gate formation. Active Si doping ~  $4\times10^{19}$  cm<sup>-3</sup> and low contact resistance of 0.5  $\Omega$ - $\mu$ m<sup>2</sup> have

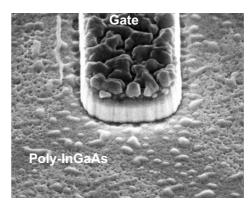

Figure 2 SEM of Poly-InGaAs regrowth.

been demonstrated by MBE and in-situ molybdenum (Mo) contacts [8]. Scaled sub 50 nm Schottky barrier FETs (HEMTs) with 1 nm EOT have been reported but have not been able to achieve the high simulated drive currents [9]. HEMTs have non-scalable source resistance because of the high bandgap barrier under the S/D contacts [10]. The Schottky gate barrier also has a higher gate leakage current than dielectrics do, making it unsuitable for VLSI applications.

The details of the process flow are provided below, but the general flow is as follows. As shown in Fig. 1, the gate was defined first by a scalable dry etch process rather than by traditional III-V lifoff techniques. The high-k dielectric was wet etched and gate was encapsulated in a SiN sidewall, followed by InGaAs source/drain regrowth by molecular beam epitaxy (MBE). Self-aligned contacts were defined by a blanket metal deposition and a height-selective etch, then the devices were mesa isolated. We shall now discuss these steps in greater detail.

First, a composite InGaAs (4 nm)/InP (2.5 nm) channel and 100 nm of InAlAs back barrier was grown by MBE on semi-insulating InP. Then the wafer was cooled to 50 °C and capped with 100 nm of As. The wafer was unloaded and transferred to an Atomic Layer Deposition (ALD) chamber, then the As cap was desorbed, and 5 nm of Al<sub>2</sub>O<sub>3</sub> dielectric was grown immediately. Next, the blanket gate stack W(50nm)/Cr(50nm)/SiO<sub>2</sub>(300nm)/Cr(50nm) was deposited. For these devices, the gate dielectric is directly on top of the thin channel, without any intentional intermediate layers. This imparts a considerable processing challenge as thin layers are prone to damage during dry etches. A damaged channel layer would result in imperfect S/D regrowth, which leads to high source resistances. Also, any pinhole introduced in the channel because of the dry etch would expose and oxidize the underlying InAlAs layer. This would again cause defect ridden S/D regrowth and high resistances. Figure 2 shows the faceted and resistive poly-InGaAs which results from regrowth on a damaged channel.

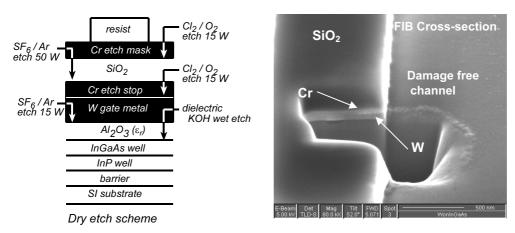

Figure 3 Dry etch scheme and FIB crosssection SEM image of a gate.

Therefore a multiple layer gate stack and alternating selective dry etch scheme was developed (Fig. 3). The top Cr layer was used as a dry etch mask after patterning it with photoresist and i-line photolithography, followed by a Cl<sub>2</sub>/O<sub>2</sub> dry etch. The Cr was removed before the channel was exposed. Next, before the SiO<sub>2</sub> was etched, the photoresist was stripped and O2 plasma etched; the SiO2 protected the channel from damage, and the aggressive O2 etch prevented organic contamination of the MBE chamber. The alternating selective dry etch scheme (Fig. 3) allows a final low power dry etch of the W layer without damaging the channel. The Al<sub>2</sub>O<sub>3</sub> dielectric was wet etched in dilute KOH solution. As a result, 300 nm long and 400 nm thick gate stacks were fabricated on 4 nm InGaAs channel. The process can be easily used to fabricate sub-50 nm features by using electron beam lithography.

A 45 nm, conformal layer of SiN<sub>x</sub> was deposited over the gates by PECVD, and a low power anisotropic etch was performed to remove the SiN<sub>x</sub> from the far field, leaving well defined sidewalls. The final SiO<sub>2</sub>/W/Cr structure with SiN<sub>x</sub> sidewalls leaves the metals unexposed in the MBE chamber during regrowth avoiding any possible metal contamination. The InGaAs channel was selectively wet etched, stopping on the InP sub-channel, and an overetch was done to etch a small amount InGaAs under the SiN<sub>x</sub> sidewall. Next the wafer was treated with 30 minute UV-Ozone forming a 1 nm sacrificial oxide. It was followed by 1 minute 1:10 HCl:DI treatment to remove the oxide, 1 minute DI rinse, and blown dry in N2. Then it was immediately loaded into MBE chamber and baked overnight at 200 °C. The wafer was atomic hydrogen cleaned at 400 °C for 30 minutes. A c(2×4) surface reconstruction was seen in reflection high energy electron diffraction (RHEED) before regrowth, indicating an epi-ready surface. Using this cleaning procedure, defect free epitaxial InGaAs films were regrown on InGaAs and showed low sheet and contact resistances [11]. A 25 nm/5 nm InGaAs/ InAs with 3.6×10<sup>19</sup> cm<sup>-3</sup> active Si doping was grown non-selectively at 400 °C. Then the wafer was then transferred to an electron beam evaporator attached to the MBE under ultra high vacuum, and 20 nm of Mo was deposited.

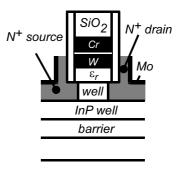

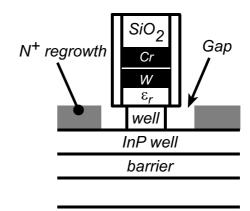

Both the InGaAs regrowth and Mo are deposited over the top of the gate, shorting the source to the drain. To remove the undesired material, the wafer was planarized by spinning photo-resist and ashed back in an inductively coupled O<sub>2</sub> plasma (ICP) until the tops of the gates were exposed. Then the Mo was dry etched in a SF<sub>6</sub>/Ar plasma, and the InGaAs layers were wet etched [11, 12]. The PR was stripped to give a self-aligned S/D MOSFET. Next S/D pads were lifted-off, and devices were mesa isolated and measured by needle probe. A schematic of the scaled InGaAs MOSFET is given in Fig. 4. The self-aligned S/D regrowth ensures the source resistance does not degrade from surface state induced depletion [13].

The RHEED was spotty during the regrowth on the MOSFET wafer, which indicated a rough surface. We attribute this to InP to InAs conversion during the initial

**Figure 4** Cross-section schematic of final device.

stage of regrowth. [14] The highly strained InAs layer relaxed, and the subsequent InGaAs growth became rough. This phenomenon was confirmed by the failure of the selective Arsenide wet etch to stop on the InP layer after regrowth. Spotty RHEED and rough InGaAs regrowth were

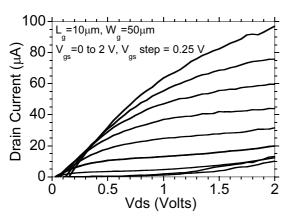

**Figure 5** Measured I<sub>d</sub>-V<sub>d</sub> of the MOSFET.

also observed on unprocessed wafers with thin InP but with no gates. A similar rough surface was observed even in chemical beam epitaxy (CBE) growth. This confirmed

A scanning electron microscope (SEM) image of the device showed a 150-200 nm gap between the  $n^+$  regrowth regions and the gate. Similar gaps in regrowth were observed on co-processed wafers with gates but without highk (Fig. 6). The gap is most likely due to shadowing by the gate during MBE regrowth and/or by a thin (nm) layer of SiN<sub>x</sub> remaining on the surface near the gate even after the sidewall etch. The gap was also observed in process monitor wafers on which no sidewall was deposited. We attribute this to shadowing by the tall gate features as well as reduced surface mobility of group III adatoms at the growth temperature (400 °C). As a result, the channel surface next to gate is starved of group III elements, resulting in a gap. Without the high doping from regrowth, the channel in the gap region is depleted of all electrons because of the pinning of Fermi-level well below the conduction band edge due to surface states. Furthermore a large undercut in Al<sub>2</sub>O<sub>3</sub> dielectric can introduce an additional depleted region between the channel and the source. Figure 7 shows

Figure 6 SEM and schematic image showing a gap in regrowth.

that the problem was a growth related issue, rather than process related contamination. Transmission line measurements (TLM) on the regrowth layer gave a high sheet resistance of 310  $\Omega$ – $\mu$ m and a contact resistance of 130  $\Omega$ – $\mu$ m? A source resistance of 300  $\Omega$ – $\mu$ m was expected from the TLM data. A low sheet resistance of 28  $\Omega$ – $\mu$ m and contact resistance of 9  $\Omega$ – $\mu$ m² were measured on a coprocessed wafer with no high-k and no InP, confirming the possibility of high quality regrowth on a processed wafer. We attribute the higher resistance observed in the MOS-FET wafer to relaxation and rough growth on the thin InP layer.

Figure 5 shows the output characteristics of a 10  $\mu m$  gate length device. The maximum drive current is  $\sim 2$   $\mu A/\mu m$  at  $V_{gs}=2.0$  V and  $V_{ds}=2.0$  V. Similar low drive currents were observed for the shorter gate length devices. The  $I_d\text{-}V_g$  characterstics showed an extremely high source resistance limited linear behavior with  $R_s\sim 10\text{-}100~k\Omega.$  The on resistance is orders of magnitude higher than the value calculated from the TLM structures.

$I_d$ - $V_{ds}$  of a device where the InGaAs channel was not etched. The breakdown voltage is 8 V consistent with an InGaAs breakdown of 20 V/ $\mu$ m [15] for total S/D to gate gap of 400 nm as seen in SEM. Thus we believe the low drive currents resulted from the undoped gaps in regrowth.

The two main reasons for the high source resistance are the inability to re-grow low resistance epitaxial InGaAs on thin InP sub-channel, and a gap region with no regrowth next to the gate. Instead of the thin InP layer, introducing a 2 nm strained In<sub>0.88</sub>Ga<sub>0.12</sub>P (InGaP) sub-channel etch stop layer allowed successful regrowth of low resistance In-GaAs [11]. A high temperature migration enhanced epitaxy (MEE) regrowth technique showed no gaps next to the gate [16]. Furthermore, a 5-10 nm thick SiN<sub>x</sub> sidewall technology is being developed. This would mean a 5-10 nm lateral extension under sidewall, so the MBE regrowth would only need to fill in a horizontal void with a 1:1 or 1:2 aspect ratio.

In summary, we developed a scalable, self-aligned, III-V MOSFET process with MBE S/D regrowth. The gate

Figure 7 Breakdown characteristics of the MOSFET.

process and H cleaning leave a 5 nm thick, clean, undamaged, epi-ready channel surface suitable for MBE or MOCVD regrowth. Working devices were fabricated with this process. The devices show low drive current because of undoped gaps between the S/D and the gate in the early devices. Improved high temperature S/D growth techniques have been developed and will be used in the next generation of devices.

**Acknowledgements** We gratefully acknowledge Semiconductor Research Corporation (SRC) for supporting this work.

## References

- P.M. Solomon and S. Laux, IEEE IEDM Tech. Dig. 2001, pp. 5.1.1-5.1.4.

- [2] Y. Sun et al., 66th DRC, Santa Barbara, 2008, pp. 41-41.

- [3] S. Koveshnikov et al., 66th DRC, Santa Barbara, 2008, pp. 43-44.

- [4] Y. Xuan et al., 66th DRC, Santa Barbara, 2008, pp. 37-38.

- [5] M. J. Rodwell, M. Wistey, U. Singisetti, G. Burek et al., 20th IEEE IPRM, 2008.

- [6] M.V. Fischetti et al., IEEE IEDM Tech. Dig., 2007, pp. 109-112.

- [7] International Technology Roadmap of Semiconductor, Front End Processes, 2007, p. 21.

- [8] U. Singisetti et al., 65th DRC, Notre Dame, 2007, pp. 149-150.

- [9] D.-H. Kim et al., IEEE IEDM Tech. Dig., 2005, pp. 767-770.

- [10] T. Takahashi et al., 19th IEEE IPRM, 2007, pp. 55-58.

- [11] M. A. Wistey et al., Electronic Materials Conference, 2008, p. Z4.

- [12] G.J. Burek et al., J. Cryst. Growth, 2008, submitted for publication.

- [13] T. Suemitsu et al., Jpn. J. Appl. Phy. 37, 1365-1372 (1998).

- [14] M.A.Wistey et al., in preparation.

- [15] Yu.A. Goldberg and N. M. Schmidt, Handbook Series on Semiconductor Parameters, Vol. 2 (World Scientific, London, 1999), pp. 62-88.

- [16] M. A. Wistey et al., 15th Int. Conf. on Molecular Beam Epitaxy, Vancouver, Canada, Aug. 2008, p 199.