#

# Conduction Mechanisms in CVD-Grown Monolayer MoS<sub>2</sub> Transistors: From Variable-Range Hopping to Velocity Saturation

G. He,<sup>†</sup> K. Ghosh,<sup>†</sup> U. Singisetti,<sup>†</sup> H. Ramamoorthy,<sup>†</sup> R. Somphonsane,<sup>‡</sup> G. Bohra,<sup>†</sup> M. Matsunaga,<sup>§</sup> A. Higuchi,<sup>§</sup> N. Aoki,<sup>§</sup> S. Najmaei,<sup>||</sup> Y. Gong,<sup>||</sup> X. Zhang,<sup>||</sup> R. Vajtai,<sup>||</sup> P. M. Ajayan,<sup>||</sup> and J. P. Bird<sup>†</sup>,\*

<sup>†</sup>Department of Electrical Engineering, University at Buffalo, The State University of New York, Buffalo, New York 14260-1900, United States

<sup>‡</sup>Department of Physics, King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

<sup>§</sup>Graduate School of Advanced Integration Science, Chiba University, 1-33 Yayoi-cho, Inage-ku, Chiba 263-8522, Japan

<sup>II</sup>Department of Materials Science and NanoEngineering, Rice University, Houston, Texas 77005, United States

### **Supporting Information**

**ABSTRACT:** We fabricate transistors from chemical vapor deposition-grown monolayer  $MoS_2$  crystals and demonstrate excellent current saturation at large drain voltages  $(V_d)$ . The lowfield characteristics of these devices indicate that the electron mobility is likely limited by scattering from charged impurities. The current–voltage characteristics exhibit variable range hopping at low  $V_d$  and evidence of velocity saturation at higher  $V_d$ . This work confirms the excellent potential of  $MoS_2$  as a possible channel-replacement material and highlights the role of multiple transport phenomena in governing its transistor action.

KEYWORDS: Molybdenum disulfide, transition metal dichalcogenides, 2D transistors, high-field transport, velocity saturation

**r**ansition-metal dichalcogenides have recently emerged as a new class of electronic materials, which, much like graphene, may be isolated in a two-dimensional (2D) form to implement a variety of novel electronic devices.<sup>1</sup> Among the materials that comprise this group, molybdenum disulfide  $(MoS_2)$  is one whose characteristics appear particularly promising for such applications. In marked contrast to graphene,  $MoS_2$  exhibits a large energy gap (1.3–1.8 eV), the direct nature of which in the monolayer form makes it attractive for not only transistor implementations but also optoelectronics. Efficient transistor action has been demonstrated for devices based on multilayer and monolayer  $MoS_2$ <sup>1-23</sup> and these devices are characterized by large (>10<sup>7</sup>) room-temperature ON-OFF ratios. They are also predicted to exhibit excellent subthreshold swing and benefit from immunity to short-channel effects.<sup>24</sup> Although the large effective mass ( $m^* =$  $(0.45m_{o})$  of the MoS<sub>2</sub> electrons means that they exhibit much lower mobility than the massless Fermions of graphene, this is not expected to be problematic for many applications involving transistor switching. In one pioneering study, MoS<sub>2</sub> transistors were used to implement small-scale integrated circuits,<sup>25</sup> providing essential Boolean functionality. Other work has demonstrated their application as sensitive photodetectors<sup>26,27</sup> capable of operating in the visible and UV ranges. Additionally, and in common with graphene, the ability to exploit valley polarization as a state variable in (monolayer) MoS<sub>2</sub> may open up the development of new "valleytronic" devices.<sup>28-30</sup>

In the vast majority of studies reported in the literature to date, MoS<sub>2</sub> transistors have been fabricated by mechanically exfoliating 2D material onto an insulating substrate from crystalline molybdenite.<sup>2–9,13–18,20,22,23,25,26</sup> Although this has the benefit of allowing rapid prototyping of individual devices, chemical routes to synthesis<sup>10–12,19,21,31–33</sup> offer the prospect of both high material yield and uniformity. Chemical vapor deposition (CVD), involving the sulfurization of molybdenum films deposited on  $Si/SiO_2$  substrates, is one such promising approach.<sup>11,12,19,31,32</sup> Depending on the initial film thickness a variety of final structures can be realized, including monolayer crystals with areas of many tens of square microns. These structures may then easily be subjected to in situ device fabrication or may be released into solution for transfer to other substrates.<sup>19</sup> Structural characterization (via Raman spectroscopy and atomic-force microscopy) of the CVD-grown crystals confirms their monolayer,<sup>11,12</sup> highly crystalline<sup>33</sup> character, making this approach particularly attractive for transistor realization. Recently, there have been some reports<sup>11,12,19</sup> of the electrical characteristics of such devices, suggesting that they are able to compete with or even exceed the performance offered by their exfoliated counterparts. In ref 21, the authors presented a detailed study of the influence of thermal annealing

Received:

March 24, 2015

Revised:

May 20, 2015

Published:

June 29, 2015

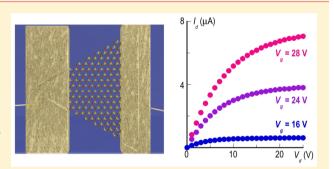

**Figure 1.** (a) Shown on the left are line scans recorded along the two white solid lines in the AFM image shown in the inset. The image is of MS2-13, and the outline of the  $MoS_2$  crystal is indicated by the white dotted line. The figure on the right is a Raman spectrum obtained using a (514.5 nm wavelength, 1  $\mu$ m spot size) laser to illuminate the channel of MS2-13. (b) Transistor curves measured at room temperature for transistor MS2-13 (shown in the false-color optical micrograph in the inset). Filled symbols are experimental data points, and solid lines represent the results of simulations (see main text for details). (c) Color contour plot showing the full evolution of  $I_d(V_d, V_g)$  for device MS2-13. (d) Expanded view of the transistor curves around  $V_d = 0$ , showing the linearity of the current over the full range of  $V_g$ .

on the transistor characteristics and showed that this allowed low-temperature (10 K) mobility values as large as 500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) to be obtained. Moreover, the authors were able to demonstrate evidence of a metal–insulator transition as a function of gate voltage, suggestive of the high electronic quality of the CVD-grown crystals.

In this Letter, we present the results of studies of the electrical properties of transistors implemented in CVD-grown, monolayer MoS<sub>2</sub>. We demonstrate, for the first time, excellent current saturation in such devices and explore the role of different transport mechanisms in governing the dependence of their drain current  $(I_d)$  on the drain  $(V_d)$  and gate  $(V_{\sigma})$ voltages. For drain voltages in the linear regime, we observe clear signatures of variable-range hopping (VRH) in the temperature (T)-dependent conduction, reminiscent of prior studies of exfoliated  $MoS_2$ .<sup>3,13</sup> The VRH weakens with an increase in the gate voltage, presumably as electrons in the channel are able to more effectively screen out the impurityrelated background potential. This behavior is accompanied at higher fields by the emergence of velocity saturation. The need to introduce the latter phenomenon arises from the strongly gate-voltage dependent character of the channel mobility  $(\mu)$ , and the saturation velocity ( $v_{sat} = 3 \times 10^6 \text{ cm s}^{-1}$ ) used to fit the experiment is found to closely match that reported in recent studies of multilayer MoS2.34 Simulations of the electrostatics within the device confirm that the velocity saturation arises from the presence of a strongly peaked electric field ( $E_{\nu}$ , where y is the direction along the channel length), which develops in the channel near the drain contact under current saturation.

Monolayer  $MoS_2$  transistors were fabricated using electronbeam lithography and metal lift-off to form Cr/Au (5 nm/50 nm) source-drain contacts to CVD-grown single MoS<sub>2</sub> crystals synthesized on commercial Si/SiO<sub>2</sub> wafers. The heavily doped Si served as the back-gate of the transistor, whereas the 280 nm thick SiO<sub>2</sub> functioned as the gate dielectric and was also used to provide optical contrast when observing the MoS<sub>2</sub> crystals under an optical microscope. (In the ultimate applications, this design could be replaced with one consisting of a top gate formed on a thin layer of high-*k* dielectric, significantly lowering the working gate-voltage range while also enhancing the mobility through "engineering" of the dielectric environment.<sup>2</sup>) The CVD growth was performed by first dispersing MoO<sub>3</sub> nanoribbons onto the Si/SiO<sub>2</sub> substrate and then sulfurizing them in a furnace.<sup>32</sup> This process resulted in the formation of triangular-shaped single crystals,  $13 \pm 2.5 \,\mu\text{m}$  on a side, whose monolayer character was confirmed by both Raman studies and atomic-force microscopy. This is indicated in Figure 1(a), in which the measured thickness of the MoS<sub>2</sub> crystal and the separation of the  $E_{2g}^1(\Gamma)$  and  $A_{1g}(\Gamma)$  Raman peaks are both consistent with earlier reports for CVD grown monolayer MoS<sub>2</sub>.<sup>11,21</sup>

The electrical characteristics of 13 different transistors were investigated for this study and were all found to exhibit fairly similar characteristics (see Table 1 of the Supporting Information, where we also define the notation used to identify the different transistors). For this reason, in our discussions here we focus on providing the results of a comprehensive study of a single device (MS2-13), which we have chosen due to its representative character. This device is shown as an inset in Figure 1(b), where the source (S) and drain (D) contacts are indicated. After fabrication, transistors were wirebonded into standard DIP packages and mounted in a cryostat, allowing

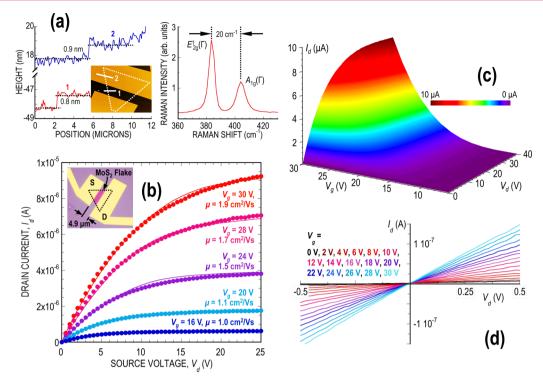

**Figure 2.** (a) Transfer characteristics of device MS2-13 ( $V_d = 0.5$  V), measured at various temperatures from 77 to 300 K. The inset plots the variation of  $I_d(V_d)$  as a function of temperature from 77 to 300 K. The gate voltage ( $V_g = 30$  V) was held fixed for these measurements. (b) The left panel shows the transfer curve of MS2-13 measured at 300 K in both sweep directions (red and blue data). In the right panel, we use a semilog plot to reveal an on-off ratio at 300 K of ~6 orders of magnitude. The measurement was made with  $V_d = 1$  V using a Keithley 4200 with a high resolution preamplifier. (c) Variation of mobility as a function of  $V_{gr}$  inferred (using eq 2) from the experimental data of (a) at different temperatures. (d) Variation of mobility as a function of temperature, inferred from the results of (c) at various gate voltages. The solid lines are trend lines that form a guide to the eye.

their electrical characteristics to be measured from 77 to 300 K with a Keithley 2400 source meter. The measurements reported here were obtained with the samples maintained under vacuum, in the dark, and in the absence of any annealing.<sup>15,21</sup> We have performed both in situ (under vacuum, 110 °C, 10<sup>-5</sup> mbar, 20 h) and ex situ (also under vacuum, 120 °C, 10<sup>-5</sup> mbar, 20 h) annealing of our devices, but in contrast to earlier reports,<sup>15,21</sup> do not find such a significant improvement in performance. The key features of transistor action (including the well-defined current saturation that we show below) are preserved after annealing, and current levels are increased by ~50%, but this improvement is much less dramatic than that achieved in refs 15 and 21. The reasons for this are unclear at present and require further investigation.

In Figure 1(b) and (c), we show measurements of the transistor curves of device MS2-13 at room temperature. Figure 1(b) shows the characteristics measured at several discrete gate voltages, along with corresponding theoretical fits (solid lines), whose details are provided further below. Figure 1(c) is a color contour that expresses the evolution of  $I_d$  as a continuous function of  $V_d$  and  $V_g$ . Both figures reveal classic transistor action with excellent saturation at high drain voltages, something that has not been demonstrated for CVD-grown MoS<sub>2</sub> devices (for which previous works have focused primarily on analyzing the transfer characteristics<sup>11,12,15,19,21</sup>). In Figure 1(d), we confirm the linear character of the current for small  $V_d$  and for a wide range of  $V_g$ . Typically, such linearity in two-

terminal measurements is taken to indicate that good ohmic contact has been achieved to the  ${\rm MoS}_2$  channel.<sup>21</sup>

In the main panel of Figure 2(a), we present measurements of the transfer  $(I_d - V_g)$  characteristic of transistor MS2-13 at a series of temperatures from 77 to 300 K. As indicated in Figure 2(b), the transfer curve showed little hysteresis as a function of sweep direction (left panel), and yielded a room-temperature on-off ratio of ~6 orders of magnitude (right panel). Regardless of the temperature in Figure 2(a), it is noted that none of the curves show the linear variation  $I_d(V_g)$  expected from a simple square-law model<sup>35</sup>

$$I_{\rm d} = \frac{W\mu}{L} \frac{\varepsilon_{\rm ox}\varepsilon_{\rm o}}{x_{\rm o}} \left[ (V_{\rm g} - V_{\rm T})V_{\rm d} - \frac{V_{\rm d}^2}{2} \right]$$

(1)

Here,  $V_{\rm T}$  is the threshold voltage, *L* is the channel length,  $x_{\rm o}$  is the oxide thickness, and  $\varepsilon_{\rm ox}$  is its dielectric constant. *W* is the channel width, which in this work is taken as the average width of the MoS<sub>2</sub> crystal at the source and drain ends.  $\mu$  is an effective channel mobility and, when this parameter is independent of gate voltage, its value can be determined from the linear relation between the drain current and the gate voltage [i.e.,  $\mu = (dI_d/dV_g)(x_o/(\varepsilon_{\rm ox} \ \varepsilon_o))(L/WV_d)$ ]. The nonlinearity of the curves in Figure 2(a) indicates that the mobility in these devices is gate-voltage dependent however, requiring us to determine  $\mu$  by solving the following expression (for details see the Supporting Information).

#### **Nano Letters**

$$\mu + (V_{\rm g} - V_{\rm T}) \frac{d\mu}{dV_{\rm g}} = \frac{L}{W} \frac{x_{\rm o}}{\varepsilon_{\rm ox} \varepsilon_{\rm o}} \frac{1}{V_{\rm d}} \frac{dl_{\rm d}}{dV_{\rm g}}$$

(2)

In Figure 2(c), we plot the variation of  $\mu(V_g)$  determined from the experimental transfer curves at various temperatures using eq 2. The mobility clearly increases in an almost linear manner with increasing  $V_g$  and is also systematically larger at higher temperatures. This latter point can be seen explicitly in Figure 2(d), where we plot the variation of  $\mu(T)$  at four different values of  $V_g$ . The behavior here is similar to that found previously for exfoliated  $MOS_2^{17}$  and is consistent with the role of charged-impurity scattering.<sup>1,5</sup> The temperature dependence of the mobility is reflected as a strong variation of the transistor curves, as we indicate in the inset to Figure 2(a). This color contour plots the  $I_d-V_d$  characteristic of transistor MS2-13 at fixed gate voltage and at a series of different temperatures. As the mobility increases with temperature, the overall current level exhibits significant growth. At every temperature, however, we observe clear signatures of the linear- and saturated-current regimes, indicating that the transistor action is robust.

Turning to the issue of the conduction mechanism in the  $MoS_2$  transistors, this is strongly dependent upon both the drain and gate voltages. For small  $V_d$ , we observe clear signatures of 2D VRH in the resistance<sup>3,13</sup>

$$R \propto R_{\rm o} \exp\left[\left(\frac{T_{\rm o}}{T}\right)^{1/3}\right]$$

(3)

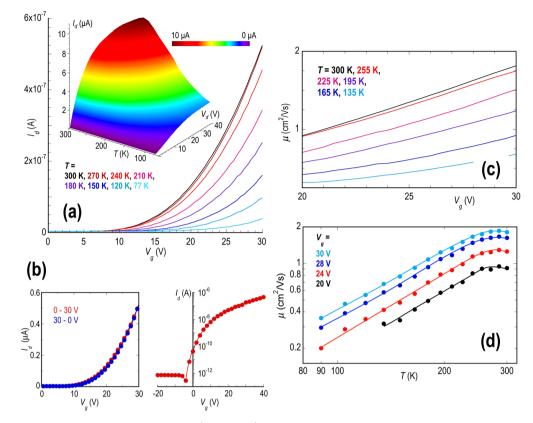

where  $R_o$  and  $T_o$  are appropriate fit parameters. In Figure 3(a), we show the variation of the resistance (*R*) as a function  $T^{-1/3}$

**Figure 3.** (a) Temperature-dependent variation in the resistance of device MS2-13 plotted to reveal the connection to VRH. A source voltage of  $V_d = 1$  V was used for these measurements. (b) Gate-voltage-dependent variation of the VRH parameter  $T_0$  (see eq 3).

(on a semilog plot) and obtain good agreement with the VRH form for a wide range of gate voltages. The resistance values plotted here were determined at  $V_d = 1$  V, well within the linear regime of transistor operation. In Figure 3(b), we plot the variation of  $T_{a1}$  inferred from the data of Figure 3(a), as a function of the gate voltage. Clearly, there is a trend for  $T_{o}$  to decrease with an increase in  $V_{g'}$  indicating that the role of the VRH is correspondingly reduced. We have already noted that the increase in mobility that we observe upon increasing temperature is indicative of the role of strong charged-impurity scattering. The related observation of VRH suggests that these charged impurities, which are presumably associated with the substrate,<sup>3</sup> also give rise to the disordered potential landscape needed for hopping to dominate. As the carrier concentration is increased by raising the gate voltage, screening of the impurity potential should then suppress the role of the hopping.  $MoS_{2}$ , like graphene, is known to be characterized by inefficient screening, particularly when prepared in few-layer form.<sup>36-39</sup> Estimates for the screening length vary, dependent upon the number of layers, but are typically in the range of several nanometers.<sup>36-39</sup> Screening of the impurity potential will therefore be incomplete in the devices, but we nonetheless expect that it should improve as the carrier concentration increases.<sup>40</sup> From our SILVACO simulations described in further detail below, we find that an increase in the gate voltage from 16 to 30 V should raise the carrier concentration in the  $MoS_2$  from 0.4 × 10<sup>12</sup> to 2.2 × 10<sup>12</sup> cm<sup>-2</sup>. According to recent theoretical work,<sup>40</sup> the increased density should lead to improved screening, and it is this phenomenon that we suggest is responsible for the modest improvements in mobility achieved in Figure 2(c).

For a more quantitative understanding of transistor action, we have simulated the performance of the devices using the SILVACO Atlas package.<sup>41</sup> Details of the calculations are provided in the Supporting Information, along with a full list of the material parameters used. The essential idea, however, is that the monolayer MoS<sub>2</sub> crystal is treated as a 0.5 nm thick film, and a classical drift-diffusion model is used to simulate the drain current. The calculations explicitly consider the triangular shape of the MoS<sub>2</sub>, and use micrographs of the actual device to determine the orientation of the crystal relative to the contacts. To account for the influence of velocity saturation, a field-dependent mobility ( $\mu(E_y)$ ) is used, such that

$$\mu(E_{y}) = \mu_{o} \left[ \frac{1}{1 + (\mu_{o} E_{y} / v_{sat})^{\beta}} \right]^{1/\beta}$$

(4)

where  $E_y$  is the electric field along the direction of current flow. Because the conduction in these devices is dominated by electrons, we take the parameter  $\beta = 2.^{42}$  The low-field mobility  $(\mu_o)$  in eq 4 is then determined by fitting the drain current to match that obtained in the linear region of the transistor curves.

Using the approach described above, we are able to successfully reproduce the experimental transistor curves of Figure 1(b). In doing so, we infer low-field mobility values in good agreement with those determined from the experimental data. This is illustrated in the inset to Figure 4(b), where we plot as discrete points the mobility values used in our simulations and compare them with those determined experimentally at room temperature. The agreement between the simulation and experiment is good, being within the error bars associated with the former. (The error bars reflect

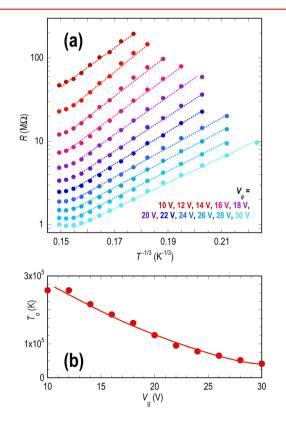

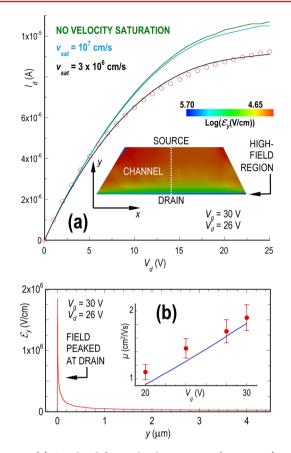

**Figure 4.** (a) Simulated fits to the drain current ( $V_g = 30$  V), using different values for  $v_{sat}$  (indicated). A saturated velocity of  $3 \times 10^6$  cm s<sup>-1</sup> is found to best fit the experimental data (open symbols). The inset plots the calculated electric field strength ( $E_y$ ) as a function of position within the channel (for  $V_g = 30$  V,  $V_d = 26$  V). The field strength is plotted on a log scale here (see color bar) and is strongly peaked at the drain end. (b) Variation of  $E_y$  as a function of position along the center line of the channel, indicated by the white dotted line. y = 0 corresponds to the drain end of the device.  $V_g = 30$  V;  $V_d = 26$  V. (inset) Comparison of experimentally determined mobility at 300 K with that used in the simulations to match the transistor curves. Device MS2-13. Solid line: experimental data. Filled symbols: simulated mobility values.

primarily the variation that arises when computing the mobility using the width of the triangular channel at its source and drain ends. The data points themselves were obtained by using an averaged valued for this width.)

An important feature revealed by our simulations is that current saturation at large  $V_{d}$  results from an interplay between channel pinch-off at the drain end and velocity saturation of electrons in the channel. At low gate voltages, where the mobility is small, the current saturation results primarily from pinch-off, whereas the converse is true at higher gate voltages. Referring to the transistor curves of Figure 1, for example, for gate voltages lower than 25 V, our simulations show that the drain current is generally consistent with a simple square-law model without the need for any velocity saturation. For larger gate voltages, however, agreement with the experiment is only possible by properly accounting for velocity saturation. This can be seen in Figure 4(a), where we show how the choice of different values for  $v_{sat}$  influences the computed current. The experimental data are plotted as open symbols in the figure, and it is clear that, with no velocity saturation (green line) or with

an assumed  $v_{sat} = 10^7 \text{ cm s}^{-1}$  (blue line), the simulated current is significantly larger than the experimental current. With  $v_{sat} = 3 \times 10^6 \text{ cm s}^{-1}$ , a value suggested in previous work on multilayer MoS<sub>2</sub> transistors,<sup>34</sup> however, the agreement is very good. In the inset to Figure 4(a), we plot a 2D surface contour of the channel field  $(E_y)$  using a logarithmic scale. The figure reveals that the velocity saturation is due to the strongly peaked nature of this field near the drain, a feature that can also be seen in Figure 4(b). Here, we plot the variation of  $E_y$  as a function of position (y) along the center line indicated by the white dotted line in the color contour of Figure 4(a). The field at the drain end approaches  $2 \times 10^6 \text{ V cm}^{-1}$ , from which value and the mobility of 1.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, we obtain an estimate for the saturated velocity of  $3.8 \times 10^6 \text{ cm} \text{ s}^{-1}$ . This is consistent with our discussion above regarding the influence of the velocity saturation on the drain current in Figure 4(a).

The mobility values determined here ( $\sim 1-10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , see Table 1 in the Supporting Information) are, in many cases, much lower than those reported elsewhere. Putting aside the fact that the estimates provided in many of these studies have been called into question by others,43 there are three primary issues that are likely at play here. First, our measurements are performed on unannealed devices, whereas thermal annealing has been demonstrated to provide improvements in the mobility.<sup>15,21</sup> Second, and perhaps more importantly, our work here shows that the mobility is strongly gate-voltage dependent, such that further increasing the gate voltage beyond the threshold can be expected to result in larger mobility values. In ref 21, for example, room-temperature mobility as large as 50–60  $\mbox{cm}^2\,\mbox{V}^{-1}\,\,\mbox{s}^{-1}$  was reported but was achieved by using back-gate voltages approaching 100 V. Finally, our two-terminal measurements may be influenced by contact resistance, which would result in an underestimate of the mobility. Although contact resistance was not included in the simulations shown in Figure 4, we have performed calculations in which the source/ drain contact resistance was increased up to  $1 \text{ k}\Omega$  (inclusion of larger values than this introduces problems with convergence) and did not observe any significant change in drain current. This can be attributed to the much lower conductance of the FET channel itself.

It is informative to compare the results of our study with those found in similar investigations of multilayer MoS<sub>2</sub> transistors. We have seen here that the current saturation in our devices arises from a combination of usual electrostatics (i.e., pinch-off at the drain) supplemented by velocity saturation that becomes important as the channel mobility improves. Current saturation has also been reported for multilayer devices<sup>5,7,18,20,34</sup> and has similarly been discussed in terms of long-channel pinch-off<sup>5</sup> and velocity saturation.<sup>34</sup> However, the much higher mobility exhibited by multilayer MoS<sub>2</sub><sup>37</sup> results in saturated current values that may be >2 orders of magnitude larger<sup>5,20,34</sup> than those reported here. In this sense, it is clear that multilayer devices are more attractive than monolayer ones for applications requiring larger drive currents. Nonetheless, in spite of its lower mobility, monolayer MoS<sub>2</sub> benefits from a larger gap (1.8 eV) than its multilayer counterpart (1.2 eV), offering the potential of a lower off current. Additionally, and in contrast to multilayer MoS<sub>2</sub>, its direct band structure makes monolayer material attractive for various light-emitting devices. In this sense, both monolayer and multilayer devices possess their own advantageous characteristics, making them suitable for very distinct applications.

In conclusion, we have fabricated transistors from CVDgrown monolayer MoS<sub>2</sub> crystals and have demonstrated wellbehaved operation in these devices. Excellent current saturation is observed at large drain voltages, and an analysis of the lowfield transport indicates that the associated mobility is likely limited by scattering from charged impurities. The dominant conduction mechanisms are strongly dependent upon both the drain and gate biases with clear evidence of VRH at small  $V_d$ . With increases in both  $V_g$  and  $V_d$ , however, a satisfactory description of the characteristics can only be achieved by invoking the role of high-field velocity saturation. The velocity saturation was shown to arise from the presence of a strongly peaked electric field near the drain end of the channel, and the value of  $v_{sat}$  inferred from our studies was shown to be consistent with reports for multilayer MoS<sub>2</sub> transistors. This work therefore confirms the excellent potential of MoS<sub>2</sub> as a possible channel-replacement material and highlights the role of multiple transport phenomena in governing its transistor action.

#### ASSOCIATED CONTENT

#### **S** Supporting Information

Information on the various devices studied, along with details of the simulation parameters, and a description of the mobility determination from the transfer characteristics. The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acs.nanolett.5b01159.

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: jbird@buffalo.edu. Phone: +1 (716) 645-1015.

#### **Author Contributions**

G.H. fabricated the MoS<sub>2</sub> transistors, and G.H., M.M., A.H., and N.A. measured their temperature-dependent electrical characteristics. G.H., R.S., H.R., G.B., S.N., R.V., and J.P.B. collaborated on the design of the experiments. K.G. performed the computational modeling of transistor performance, working in collaboration with U.S., G.H., and J.P.B. CVD growth of MoS<sub>2</sub> crystals was performed by S.N. in collaboration with R.V. and P.M.A. Y.G. and X.Z. performed AFM and Raman microscopy of the fabricated devices.

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

Device fabrication and electrical characterization were performed in the group of J.P.B. under the support of the U.S. Department of Energy, Office of Basic Energy Sciences, Division of Materials Sciences and Engineering (Award # DE-FG02-04ER46180). Computations of MoS<sub>2</sub> transistor operation were undertaken in the group of U.S. and were supported by the Department of Electrical Engineering at the University at Buffalo. CVD growth of the MoS<sub>2</sub> was performed in the group of P.M.A. and was supported by the U.S. Army Research Office MURI Grant W911NF-11-10362.

## REFERENCES

(1) Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Nat. Nanotechnol. **2012**, *7*, 699–712.

- (2) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- (3) Ghatak, S.; Pal, A. N.; Ghosh, A. ACS Nano 2011, 5, 7707-7712.

(4) Castellanos-Gomez, A.; Barkelid, M.; Goossens, A. M.; Calado, V.

E.; van der Zant, H. S.; Steele, G. A. *Nano Lett.* 2012, *12*, 3187–3192.

(5) Kim, S.; Konar, A.; Hwang, W.-S.; Lee, J. H.; Lee, J.; Yang, J.;

Jung, C.; Kim, H.; Yoo, J.-B.; Choi, J.-Y.; Jin, Y. W.; Lee, S. Y.; Jena, D.; Choi, W.; Kim, K. Nat. Commun. **2012**, *3*, 1011.

(6) Zhang, Y.; Ye, J.; Matsuhashi, Y.; Iwasa, Y. Nano Lett. 2012, 12, 1136–1140.

(7) Qiu, H.; Pan, L.; Yao, Z.; Li, J.; Shi, Y.; Wang, X. Appl. Phys. Lett. **2012**, 100, 123104.

(8) Late, D. J.; Liu, B.; Matte, R. H. S. S.; Dravid, V. P.; Rao, C. N. R. ACS Nano **2012**, *6*, 5635–5641.

(9) Liu, H.; Neal, A. T.; Ye, P. D. ACS Nano 2012, 6, 8563–8569.

(10) Sik Hwang, W.; Remskar, M.; Yan, R.; Kosel, T.; Kyung Park, J.; Jin Cho, B.; Haensch, W.; Xing, H.; Seabaugh, A.; Jena, D. Appl. Phys. Lett. 2013, 102, 043116.

(11) Amani, M.; Chin, M. L.; Birdwell, A. G.; O'Regan, T. P.; Najmaei, S.; Liu, Z.; Ajayan, P. M. *Appl. Phys. Lett.* **2013**, *102*, 193107.

(12) Wu, W.; De, D.; Chang, S.-C.; Wang, Y.; Peng, H.; Bao, J.; Pei, S.-S. *Appl. Phys. Lett.* **2013**, *102*, 142106.

(13) Jariwala, D.; Sangwan, V. K.; Late, D. J.; Johns, J. E.; Dravid, V. P.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. *Appl. Phys. Lett.* **2013**, *102*, 173107.

(14) Walia, S.; Balendhran, S.; Wang, Y.; Ab Kadir, R.; Sabrin Zoolfakar, A.; Atkin, P.; Zhen Ou, J.; Sriram, S.; Kalantar-Zadeh, K.; Bhaskaran, M. *Appl. Phys. Lett.* **2013**, *103*, 232105.

(15) Baugher, B. W. H.; Churchill, H. O. H; Yang, Y.; Jarillo-Herrero, P. Nano Lett. **2013**, 13, 4212–4216.

(16) Qiu, H.; Xu, T.; Wang, Z.; Ren, W.; Nan, H.; Ni, Z.; Chen, Q.; Yuan, S.; Miao, F.; Song, F.; Long, G.; Shi, Y.; Sun, L.; Wang, J.; Wang, X. Nat. Commun. **2013**, *4*, 2642.

(17) Radisavljevic, B.; Kis, A. Nat. Mater. 2013, 12, 815-820.

(18) Chang, H.-Y.; Zhu, W.; Akinwande, D. Appl. Phys. Lett. 2014, 104, 113504.

(19) Amani, M.; Chin, M. L.; Mazzoni, A. L.; Burke, R. A.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Dubey, M. *Appl. Phys. Lett.* **2014**, *104*, 203506.

(20) Kwon, H.-J.; Jang, J.; Kim, S.; Subramanian, V.; Grigoropoulos, C. P. Appl. Phys. Lett. **2014**, 105, 152105.

(21) Schmidt, H.; Wang, S.; Chu, L.; Toh, M.; Kumar, R.; Zhao, W.; Castro Neto, A. H.; Martin, J.; Adam, S.; Özyilmaz, B.; Eda, G. *Nano Lett.* **2014**, *14*, 1909–1913.

(22) Yuan, H.; Cheng, G.; You, L.; Zhu, H.; Li, W.; Kopanski, J. J.;

Obeng, Y. S.; Hight Walker, A. R.; Gundlach, D. J.; Richter, C. A.;

Ioannou, D. E.; Li, Q. ACS Appl. Mater. Interfaces 2015, 7, 1180–1187.

(23) Zhang, F.; Appenzeller, J. Nano Lett. 2015, 15, 301–306.

(24) Yoon, Y.; Ganapathi, K.; Salahuddin, S. Nano Lett. 2011, 11, 3768-3773.

(25) Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. *Nano Lett.* **2012**, *12*, 4674–4680.

(26) Lopez-Sanchez, O.; Lembke, D.; Kayci, M.; Radenovic, A.; Kis, A. Nat. Nanotechnol. **2013**, *8*, 497–501.

(27) Yin, Z.; Li, H.; Li, H.; Jiang, L.; Shi, Y.; Sun, Y.; Lu, G.; Zhang, Q.; Chen, X.; Zhang, H. ACS Nano **2012**, *6*, 74–80.

(28) Zeng, H.; Dai, J.; Yao, W.; Xiao, D.; Cui, X. Nat. Nanotechnol. 2012, 7, 490–493.

(29) Mak, K. F.; He, K.; Shan, J.; Heinz, T. F. Nat. Nanotechnol. 2012, 7, 494–498.

(30) Cao, T.; Wang, G.; Han, W.; Ye, H.; Zhu, C.; Shi, J.; Niu, Q.; Tan, P.; Wang, E.; Liu, B.; Feng, J. Nat. Commun. 2012, 3, 887.

(31) Lee, Y. H.; Zhang, X.-Q.; Zhang, W.; Chang, M.-T.; Lin, C.-T.; Chang, K. D.; Yu, Y.-C.; Wang, J. T.-W.; Chang, C.-S.; Li, L.-J.; Lin, T. W. *Adv. Mater.* **2012**, *24*, 2320–2325.

(32) Zhan, Y.; Liu, Z.; Najmaei, S.; Ajayan, P. M.; Lou, J. Small 2012, 8, 966–971.

(33) van der Zande, A. M.; Huang, P. Y.; Chenet, D. A.; Berkelbach, T. C.; You, Y.; Lee, G.-H.; Heinz, T. F.; Reichman, D. R.; Muller, D. A.; Hone, J. C. *Nat. Mater.* **2013**, *12*, 554–561.

(34) Fiori, G.; Szafranek, B. N.; Iannaccone, G.; Neumaier, D. Appl. Phys. Lett. 2013, 103, 233509.

- (35) Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices, 3<sup>rd</sup> ed.; John Wiley & Sons, Inc., 2007.

- (36) Castellanos-Gomez, A.; Cappelluti, E.; Roldan, R.; Agrait, N.; Guinea, F.; Rubio-Bollinger, G. *Adv. Mater.* **2013**, *25*, 899–903.

(37) Das, S.; Appenzeller, J. Phys. Status Solidi RRL 2013, 7, 268-273.

(38) Li, Y.; Xu, C.-Y.; Zhen, L. Appl. Phys. Lett. 2013, 102, 143110.

(39) Yu, W. J.; Liu, Y.; Zhou, H.; Yin, A.; Li, Z.; Huang, Y.; Duan, X. Nat. Nanotechnol. 2013, 8, 952–958.

(40) Ma, N.; Jena, D. Phys. Rev. X 2014, 4, 011043.

(41) Atlas user manual. www.silvaco.com (accessed March 21, 2014), SILVACO, Inc..

- (42) Thomas, R. E. Proc., IEEE 1967, 55, 2192-2193.

- (43) Fuhrer, M. S.; Hone, J. Nat. Nanotechnol. 2013, 8, 146-147.