# Interface characterization of atomic layer deposited high-k on non-polar GaN

Ye Jia, Ke Zeng, and Uttam Singisetti

Citation: Journal of Applied Physics **122**, 154104 (2017); doi: 10.1063/1.4986215 View online: http://dx.doi.org/10.1063/1.4986215 View Table of Contents: http://aip.scitation.org/toc/jap/122/15 Published by the American Institute of Physics

## Articles you may be interested in

Initial leakage current paths in the vertical-type GaN-on-GaN Schottky barrier diodes Applied Physics Letters **111**, 122102 (2017); 10.1063/1.4994627

Molecular beam epitaxial growth and characterization of AIN nanowall deep UV light emitting diodes Applied Physics Letters **111**, 101103 (2017); 10.1063/1.4989551

Evolution and prevention of meltback etching: Case study of semipolar GaN growth on patterned silicon substrates Journal of Applied Physics **122**, 105108 (2017); 10.1063/1.5001914

Defect quasi Fermi level control-based C<sub>N</sub> reduction in GaN: Evidence for the role of minority carriers Applied Physics Letters **111**, 152101 (2017); 10.1063/1.5000720

Valence and conduction band offsets of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/AlN heterojunction Applied Physics Letters **111**, 162105 (2017); 10.1063/1.5003930

Optical and structural study of deformation states in the GaN/AIN superlattices Journal of Applied Physics **122**, 155302 (2017); 10.1063/1.4999175

# Interface characterization of atomic layer deposited high-k on non-polar GaN

Ye Jia, Ke Zeng, and Uttam Singisetti<sup>a)</sup>

Department of Electrical Engineering, University at Buffalo, The State University of New York, Buffalo, New York 14260, USA

(Received 2 June 2017; accepted 30 September 2017; published online 18 October 2017)

The interface properties between dielectrics and semiconductors are crucial for electronic devices. In this work, we report the electrical characterization of the interface properties between atomic layer deposited  $Al_2O_3$  and  $HfO_2$  on non-polar a-plane (1120) and m-plane (1100) GaN grown by hybrid vapor phase epitaxy. A metal oxide semiconductor capacitor (MOSCAP) structure was used to evaluate the interface properties. The impact of annealing on the interface properties was also investigated. The border trap in the oxide, characterized by the capacitance-voltage (C-V) hysteresis loop, was low. The interface state density  $(D_{it})$ , extracted using the ac conductance method, is in the range of  $0.5 \times 10^{12}$ /cm<sup>2</sup> eV to  $7.5 \times 10^{11}$ /cm<sup>2</sup> eV within an energy range from 0.2 eV to 0.5 eV below the conduction band minimum. The m-plane GaN MOSCAPs exhibited better interface properties than the a-plane GaN MOSCAPs after annealing. Without annealing, Al<sub>2</sub>O<sub>3</sub> dielectrics had higher border trap density and interface state density compared to HfO<sub>2</sub> dielectrics. However, the annealing had different impacts on Al<sub>2</sub>O<sub>3</sub> dielectrics as compared to HfO<sub>2</sub>. Our results showed that the annealing degraded the quality of the interface in HfO2, but it improved the quality of the interface in  $Al_2O_3$  devices. The annealing also reduced the positive trapped oxide charge, resulting in a shift of C-V curves towards the positive bias region. *Published by AIP Publishing*. https://doi.org/10.1063/1.4986215

## I. INTRODUCTION

GaN, a wide bandgap semiconductor, has been extensively studied for a variety of applications such as power amplifiers, power conversion devices, and light-emitting diodes (LEDs) because of its large bandgap, high electron mobility, high electron velocity, high breakdown voltage, and the capability of forming various alloys.<sup>1–5</sup> GaN is a polar material with a wurtzite crystal structure, which results in a large polarization field along the *c*-axis of the crystal<sup>6,7</sup> which is the traditional direction of the GaN crystal growth. The polarization field has been used for polarization doping of heterostructures that show high electron mobilities.<sup>8,9</sup> The polarization field has been exploited to increase the hole density in the p-type AlGaN/GaN heterojunction.<sup>10</sup> However, for optoelectronic devices, the separation of electron and hole wavefunctions due to the polarization field leads to a reduction of the radiative emission rate.<sup>4,7,11</sup> Moreover, the p-type doping flexibility is reduced in polar GaN because of the polarity inversion caused by the high Mg flux for achieving a high Mg concentration.<sup>12-14</sup> In recent years, novel non-polar GaN has drawn a lot of attention for optoelectronic and electronic devices.<sup>15–18</sup> Unlike the conventional polar GaN, the polarization field is absent in the non-polar GaN crystal along the nonpolar direction.<sup>7,19</sup> The absence of the polarization field in non-polar GaN benefits both optoelectronic and electronic devices.<sup>20,21</sup> Non-polar optoelectronic device performance has been greatly improved as compared to that of polar optoelectronics devices, with reduction of the efficiency droop.<sup>11,22,23</sup> The density function theory (DFT) predicts that the Fermi level in p-type non-polar GaN is unpinned,<sup>24</sup> which could reduce the contact resistance to p-type GaN.<sup>14</sup> We have previously reported that the Fermi level in n-type non-polar m-plane GaN was pinned close to mid-gap ( $\sim$ 2.4 eV above the valence band maximum).<sup>25</sup> The low contact resistance to p-type GaN is beneficial to heterostructure bipolar transistors (HBTs) and p-channel devices.<sup>26,27</sup> A normally off p-type semi-polar GaN power device with high breakdown voltage was demonstrated,<sup>28</sup> which can also benefit from the low contact resistance to p-type GaN.

Dielectrics are used as the gate barrier and passivation layer in electronic devices. It is important to quantitatively understand the interface electrical properties between the dielectric layer and non-polar GaN for electronic applications. Atomic layer deposition (ALD) has been widely used for depositing a low interface state density high-k gate dielectric layer on silicon, III-V materials, and emerging 2D materials.<sup>10,29–33</sup> The interface properties of ALD-dielectric/polar GaN in terms of interface state density  $(D_{it})$  have been studied by the photo-assisted capacitance-voltage (CV) technique,<sup>34</sup> the conductance method,<sup>34,35</sup> and deep-level transient spectroscopy.<sup>36</sup> The impact of thermal annealing on the interface properties has also been investigated.<sup>34</sup> However, there is no report on the interface properties between dielectrics and non-polar GaN. The band offsets between ALD-Al<sub>2</sub>O<sub>3</sub> and m-plane GaN characterized by x-ray photoelectron spectroscopy have been reported,<sup>25</sup> including the structural characterization. In this work, we evaluated the interface state density and border trap density in ALD deposited high-k dielectrics on a-plane and m-plane non-polar GaN.

## **II. EXPERIMENT DETAILS**

The non-polar *a*-plane and *m*-plane bulk GaN wafers were prepared at Kyma technologies Inc. The non-polar GaN substrates were sliced from polar *c*-plane GaN which

a)uttamsin@buffalo.edu

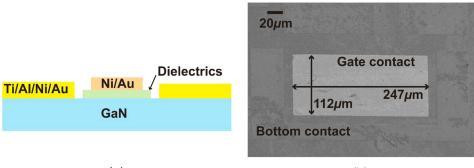

was grown by hybrid vapor phase epitaxy (HVPE). The root mean square (rms) roughness of the a-plane and m-plane GaN substrates was 0.3 nm and 0.5 nm, respectively. The van der Pauw Hall measurement gave an n-type conductivity with a doping density of  $\sim 1 \times 10^{16}$ /cm<sup>3</sup> for both samples. The metal-oxide-semiconductor (MOSCAP) structures were fabricated to study the interface properties. It is necessary to form ohmic contacts to GaN in order to study the frequency dependent capacitance-voltage profiles. It has been reported that the contact resistance to GaN can be reduced by reactive ion etching and post deposition annealing.<sup>37</sup> The MOSCAP structure is shown in Fig. 1(a). After standard solvent and HF cleaning, the wafers were exposed to an inductively coupled plasma reactive ion etcher (ICP-RIE) with a gas mixture of BCl<sub>3</sub> and Cl<sub>2</sub>.<sup>25</sup> The Ti/Al/Ni/Au bottom ohmic contact was patterned by electron-beam lithography (EBL) and the lift-off process. Next, the wafers were subjected to a rapid thermal annealing (RTA) process at 950 °C for 1 min in N<sub>2</sub> ambient. Afterwards, the high-k dielectric layer was deposited using a thermal ALD tool. Here, we investigated two high-k dielectrics, Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>. Al<sub>2</sub>O<sub>3</sub> was deposited at 300 °C with trimethylaluminum (TMA) and H<sub>2</sub>O. HfO<sub>2</sub> was deposited at 150 °C with tetrakis(dimethylamido)hafnium (TDMAH) and H<sub>2</sub>O. A top gate contact was formed by EBL and the lift-off process. The bottom contact was opened by an alumina etchant for Al<sub>2</sub>O<sub>3</sub>-MOSCAPs and dilute HF for HfO<sub>2</sub>-MOSCAPs. To investigate the impacts of annealing on the interface properties, the Al<sub>2</sub>O<sub>3</sub>-MOSCAPs were annealed in N2 ambient at 500 °C for 1 min, while the HfO2-MOSCAPs were annealed in vacuum at 350 °C for 1 min.

The capacitance of the MOSCAPs was measured using an Agilent 4294A precise impedance analyzer with a HP42941 impedance probe. Border traps that are close to the interface of dielectric/GaN can respond to the Fermi level and affect the device performance. The border trap density ( $N_{bt,tot}$ ) is calculated from the capacitance-voltage (C-V) hysteresis loop by the following equation:<sup>34</sup>

$$N_{bt,tot} = \frac{1}{qA} \int_{V_1}^{V_2} |C_{up} - C_{dwn}| dV,$$

(1)

where V is the applied bias, q is the charge unit, A is the device area, and  $C_{up}$  and  $C_{dwn}$  are the measured capacitances when the bias is swept from the negative to the positive region and vice versa. The interface state density  $(D_{it})$  is calculated using the conductance method which exploits the

change in occupancy of interface states.<sup>35</sup> Using the parallel conductance model,  $D_{it}$  can be estimated by the following equation:<sup>35</sup>

$$D_{it} = \frac{2.5}{qA} \left(\frac{G_p}{\omega}\right)_{max},\tag{2}$$

where  $\omega$  is the probing frequency in rad/s. The parallel conductance,  $(G_p/\omega)$ , can be calculated from the measured capacitance  $(C_m)$  and conductance  $(G_m)$  directly by the ignoring series resistance<sup>38</sup>

$$\frac{\langle G_p \rangle}{\omega} = \frac{\omega C_{ox}^2 G_m}{G_m^2 + \omega^2 (C_{ox} - C_m)^2},\tag{3}$$

where  $C_{ox}$  is the oxide capacitance. Since the change in occupancy only occurs when the energy of interface states is close to the Fermi level, the relative energy level ( $\Delta E$ ) of the interface states can be found by the SRH model<sup>35</sup>

$$\Delta E = k_B T \ln \left(\tau \sigma v_t N_c\right),\tag{4}$$

where  $k_B$  is the Boltzmann constant, *T* is the temperature,  $\tau$  is the lifetime of the interface states,  $\sigma$  is the capture cross section of the interface states,  $v_t$  is the thermal velocity, and  $N_c$  is the effective density of state in the conduction band.

#### **III. RESULTS AND DISCUSSION**

#### A. Al<sub>2</sub>O<sub>3</sub>/m-plane GaN MOSCAP

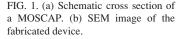

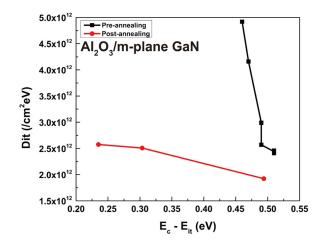

Figures 2(a) and 2(b) show the high frequency (1 MHz) C-V hysteresis loop of the Al<sub>2</sub>O<sub>3</sub>/m-plane GaN MOSCAP measured at 1 MHz before and after annealing. The inset shows the distribution of the border traps as a function of gate bias. After annealing, there was a positive shift of the C-V curve, which indicated a reduction of positive trapped oxide charge. The total density of border traps reduced from  $1.8 \times 10^{11}$ /cm<sup>2</sup> to  $0.86 \times 10^{11}$ /cm<sup>2</sup> with annealing. Figures 3(a) and 3(b) show the frequency-dependent C-V profiles before and after annealing. The C-V curves were measured from 10 kHz to 1 MHz. In the negative bias region, only marginal frequency dispersion was observed, indicating a low  $D_{it}$ . However, after annealing, a relatively larger dispersion was observed when the gate bias was positive, as shown in Fig. 3(b). Therefore, we could expect a high  $D_{it}$  in the positive gate bias region. The knowledge of  $C_{ox}$  was required to extract  $D_{it}$ ; however, we were unable to measure

FIG. 2. C-V hysteresis loop of the Al<sub>2</sub>O<sub>3</sub>/m-plane GaN device (a) before annealing and (b) after annealing. The insets show the distribution of the border traps as a function of gate bias. After annealing, the C-V curves shifted towards the positive bias region. Reprinted with permission from Y. Jia *et al.*, Phys. Status Solidi B **254**, 1600681 (2017). Copyright 2017 John Wilev and Sons.

FIG. 3. Frequency-dependent C-V curves of the  $Al_2O_3/m$ -plane GaN device (a) before annealing and (b) after annealing. A small frequency dispersion was observed at negative bias. Reprinted with permission from Y. Jia *et al.*, Phys. Status Solidi B **254**, 1600681 (2017). Copyright 2017 John Wiley and Sons.

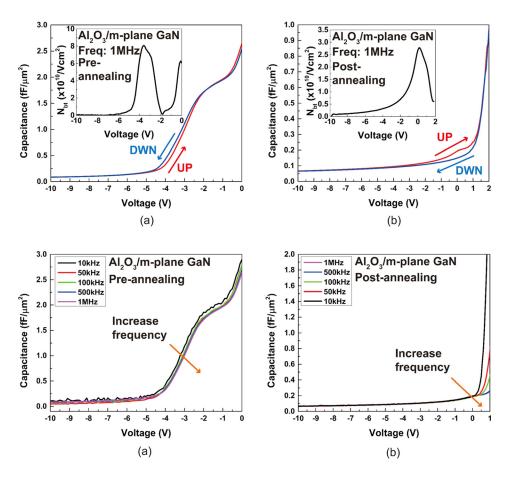

it directly from the GaN MOSCAPs due to the high leakage current in the accumulation region, so we assumed that the  $C_{ox}$  of GaN devices would be the same as that of Si devices that were fabricated simultaneously. Figure 4(a) shows the calculated conductance peaks  $(G_p/\omega)$  as a function of frequency using Eq. (3). The  $G_p/\omega$  peaks were measured from -2 V to -10 V. It can be seen that when the bias was small (-2 V to -5 V), the peak was modulated by the gate bias. The peak shifted to lower frequency with the increasing gate bias. When the gate bias was sufficiently large, the peak was pinned at ~200 Hz. The pinning of the  $G_p/\omega$  peaks can be attributed to the bulk traps. Figure 4(b) shows the calculated conductance peak as a function of frequency after annealing. As indicated in Fig. 3, because the C-V curves shifted to the positive bias region after annealing, the  $G_p/\omega$  peaks after annealing were measured from +2 V to -2 V. Similar to the  $G_p/\omega$  peak before annealing, the conductance peak was modulated by bias. The peak shifted from 6 MHz to 400 Hz when the bias changed from 2 V to 0 V. When the bias moved to the negative region, the peak shifted to a very low frequency which was outside of the measurable range of the instrument at room temperature. Figure 5 shows the calculated  $D_{it}$  as a function of its energy level using Eq. (4) before and after annealing. Before annealing,  $D_{it}$  ranged from  $\sim 2.5 \times 10^{12} \text{ cm}^{-2} \text{ V}^{-1}$  to  $\sim 5.0 \times 10^{12} \text{ cm}^{-2} \text{ V}^{-1}$  and its energy ranged from 0.51 eV to 0.46 eV. Our reported  $D_{it}$  values were slightly higher than the  $D_{it}$  of Al<sub>2</sub>O<sub>3</sub>/c-plane GaN reported by Winzer *et al.*<sup>34</sup> in the comparable energy range. After annealing,  $D_{it}$  was in the range of  $2.0 \times 10^{12} \text{ cm}^{-2} \text{ V}^{-1}$  to  $2.5 \times 10^{12} \text{ cm}^{-2} \text{ V}^{-1}$  and  $E_{it}$  was closer to conduction band minimum (CBM) compared to before annealing. At an  $E_{it}$  of greater than 0.45 eV,  $D_{it}$  decreased from  $5 \times 10^{12} \text{ cm}^{-2} \text{ V}^{-1}$  after annealing.

FIG. 4.  $G_p/\omega$  peak of the Al<sub>2</sub>O<sub>3</sub>/mplane GaN device (a) before annealing and (b) after annealing. The peak was modulated by bias. The peaks were pinned at ~200 Hz when the bias was greater than -5 V.

FIG. 5. The calculated  $D_{ii}$  of Al<sub>2</sub>O<sub>3</sub>/m-plane GaN devices before and after annealing.  $D_{ii}$  was found to be in the range of  $2.5 \times 10^{12}$ /cm<sup>2</sup> eV to  $5.0 \times 10^{12}$ /cm<sup>2</sup> eV without annealing. The annealing process reduced  $D_{ii}$ .

#### B. HfO<sub>2</sub>/m-plane GaN MOSCAP

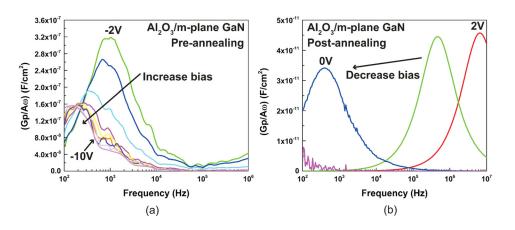

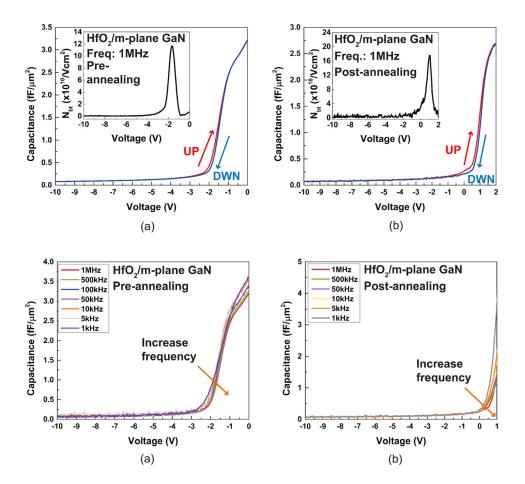

Figures 6(a) and 6(b) show the C-V hysteresis loop of the HfO<sub>2</sub>/m-plane GaN MOSCAP measured at 1 MHz before and after annealing. Similar to the Al<sub>2</sub>O<sub>3</sub>/m-plane GaN MOSCAPs, there was a positive shift in the C-V curve after annealing. The inset shows the calculated distribution of border traps as a function of gate bias. The border trap density was calculated to be  $1.0 \times 10^{11}$ /cm<sup>2</sup> before annealing and  $1.9 \times 10^{11}$ /cm<sup>2</sup> after annealing. The annealing process slightly increased the density of border traps. Figures 7(a) and 7(b) show the frequency-dependent C-V profiles

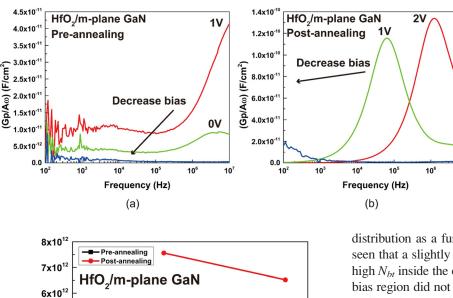

measured from 1 kHz to 1 MHz pre- and post-annealing. Similar to Al<sub>2</sub>O<sub>3</sub>/m-plane GaN MOSCAPs, a small frequency dispersion in C-V curves was observed before annealing. After annealing, C-V curves showed a large dispersion in the positive gate bias region, indicating a high  $D_{it}$ . Figures 8(a) and 8(b) show the  $G_p/\omega$  peaks as a function of frequency before and after annealing. In Fig. 8(a), it can be seen that the position of the  $G_p/\omega$  peak at a gate bias of 1 V was higher than 10 MHz which exceeded the measurement capability and a partial peak was observed. While the position of the  $G_p/\omega$  peak at a gate voltage of -1 V was lower than the lower limit of the measurement frequency (100 Hz not shown). Only one clear  $G_p/\omega$  peak was observed at a bias of 0V, which suggested that the interface states were close to CBM and mid-gap. Similarly, in Fig. 8(b), after annealing, there was no clear or complete  $G_p/\omega$  peak when the bias became negative. Figure 9 shows the calculated  $D_{it}$  before and after annealing within the measurable range. Before annealing,  $D_{it}$  was about  $2.5 \times 10^{12}$ /cm<sup>2</sup> eV<sup>-1</sup> to  $0.7 \times 10^{12}$ /  $\text{cm}^2 \text{eV}^{-1}$  at an  $E_{it}$  in the range of 0.23–0.25 eV. As we mentioned above, the interface states were close to CBM. After annealing,  $D_{it}$  increased to  $\sim 7.5 \times 10^{12}$ /cm<sup>2</sup> eV at an  $E_{it}$  of 0.28 eV and  $\sim 6.5 \times 10^{12}$ /cm<sup>2</sup> eV at an  $E_{it}$  of 0.35 eV. The annealing process increased  $D_{it}$ . The effect of annealing on HfO<sub>2</sub>-MOSCAPs was opposite to that of on Al<sub>2</sub>O<sub>3</sub>-MOSCAPs. It should be noted that a temperature dependent conductance measurement is necessary to probe more of the interface states because at room temperature the measurable range of  $E_{it}$  is limited.

FIG. 6. C-V hysteresis loop of the  $HfO_2/m$ -plane GaN device (a) before annealing and (b) after annealing. The insets show the distribution of the border traps as a function of gate bias. After annealing, the C-V curves shifted towards the positive bias region.

FIG. 7. Frequency-dependent C-V curves of the  $HfO_2/m$ -plane GaN device (a) before annealing and (b) after annealing. A small frequency dispersion was observed at negative bias.

5x10<sup>12</sup>

4x10<sup>12</sup>

3x10<sup>12</sup>

2x10<sup>12</sup>

1x10<sup>12</sup>

0.22

0.24

0.26

D<sub>it</sub> (/cm<sup>2</sup>eV)

0.32

0.34

0.30

E<sub>c</sub> - E<sub>it</sub> (eV)

0.36

FIG. 9. The calculated  $D_{ii}$  of HfO<sub>2</sub>/m-plane GaN devices before and after annealing.  $D_{ii}$  was found to be in the range of  $6 \times 10^{11}$ /cm<sup>2</sup> eV to  $2.5 \times 10^{12}$ / cm<sup>2</sup> eV without annealing. The annealing process increased  $D_{ii}$ .

0.28

# C. Al<sub>2</sub>O<sub>3</sub>/a-plane GaN MOSCAP and HfO<sub>2</sub>/a-plane GaN MOSCAP

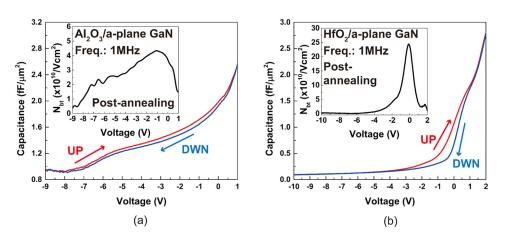

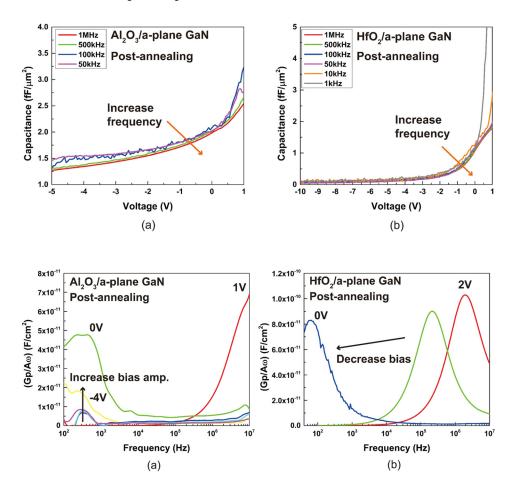

Unlike the m-plane GaN MOSCAPs, the a-plane GaN MOSCAPs were characterized after the annealing process because the MOSCAPs showed a high gate leakage current before annealing. The devices were subjected to the same annealing condition as m-plane GaN MOSCAPs. Figures 10(a) and 10(b) show the C-V hysteresis loop of the Al<sub>2</sub>O<sub>3</sub>/a-plane GaN MOSCAP and HfO<sub>2</sub>/a-plane GaN MOSCAP, respectively. The insets show the corresponding border trap

FIG. 8.  $G_p/\omega$  peak of the HfO<sub>2</sub>/mplane GaN device (a) before annealing and (b) after annealing. The peak was modulated by bias. Only two peaks were observed before and after annealing.

distribution as a function of gate bias. In Fig. 10(a), it can be seen that a slightly large dispersion was observed, indicating a high  $N_{bt}$  inside the oxide. The C-V curves in the large negative bias region did not show a depletion behavior, which could be attributed to the high density of interface states and/or oxide traps. In contrast, in Fig. 10(b), the HfO<sub>2</sub>/a-plane GaN MOSCAP showed a flat C-V curve in the large negative bias region. However, its C-V hysteresis loop exhibited a large dispersion between gate biases of 1 V and -3 V, indicating a high  $N_{bt}$ . The inset of Fig. 10(a) showed a very broad distribution of  $N_{bt}$ , giving an  $N_{bt}$ , tot of  $2.7 \times 10^{11}$ /cm<sup>2</sup>, whereas the inset of Fig. 10(b) showed a narrow distribution of  $N_{bt}$ . However, the peak reached a high value of  $2.5 \times 10^{11}$ /cm<sup>2</sup>, resulting in a total  $N_{bt, tot}$  of  $4.3 \times 10^{11}$ /cm<sup>2</sup>. Figures 11(a) and 11(b) show the frequency-dependent C-V curves of Al<sub>2</sub>O<sub>3</sub>/a-plane GaN and HfO2/a-plane GaN MOSCAPs after annealing. The measured frequencies for the Al2O3/a-plane GaN MOSCAP were from 50 kHz to 1 MHz and for the HfO<sub>2</sub>/a-plane GaN MOSCAP were from 1 kHz to 1 MHz. The bias of the  $Al_2O_3/$ a-plane GaN MOSCAP was swept from 1 V to -5 V due to high leakage current at low frequency. In Fig. 11(a), we can see that there was a large frequency dispersion in the negative bias region, suggesting a high  $D_{it}$ . However, the HfO<sub>2</sub>/a-plane GaN MOSCAP revealed large dispersion in the positive bias region. Figures 12(a) and 12(b) show the  $G_p/\omega$  peaks of Al<sub>2</sub>O<sub>3</sub>/a-plane GaN and HfO<sub>2</sub>/a-plane GaN MOSCAPs. In Fig. 12(a), when the bias was greater than 1 V, the peak located at a frequency of >10 MHz. With decreasing bias to the negative region, the peak shifted to lower frequency and it was pinned at  $\sim$  300 Hz when the bias was greater than -2 V. Figure 12(b)

10

FIG. 10. C-V hysteresis loop of (a) the  $Al_2O_3/a$ -plane GaN device and (b)  $HfO_2/a$ -plane GaN device after annealing. The insets show the distribution of border traps as a function of bias.  $N_{bt, tot}$  was higher than that of the m-plane GaN device.

FIG. 11. Frequency-dependent C-V curves of (a) the  $Al_2O_3/a$ -plane GaN device and (b) HfO<sub>2</sub>/a-plane GaN device after annealing. The  $Al_2O_3/a$ -plane GaN device showed relatively large frequency dispersion compared to the HfO<sub>2</sub>/a-plane GaN device in the negative bias region.

FIG. 12.  $G_p/\omega$  peak of (a) the Al<sub>2</sub>O<sub>3</sub>/aplane GaN device and (b) HfO<sub>2</sub>/mplane GaN device after annealing. The peak was modulated by bias. The  $G_p/\omega$ peak was pinned at ~200 Hz probably caused by bulk trap loss when bias was greater than -1 V.

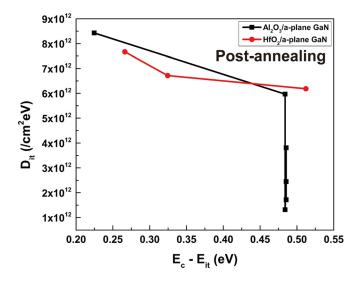

clearly shows voltage modulated  $G_p/\omega$  peaks from 2 V to 0 V. However, when the bias was in the negative region, the  $G_p/\omega$  peak was out of the measurable range. Figure 13 shows the calculated  $D_{it}$  of the MOSCAPs. The  $D_{it}$  of the Al<sub>2</sub>O<sub>3</sub>/GaN device was >8.5 × 10<sup>12</sup>/cm<sup>2</sup> eV at an  $E_{it}$  of 0.23 eV and ~1.2 × 10<sup>12</sup>/cm<sup>2</sup> eV at an  $E_{it}$  of 0.48 eV. When the gate bias changed from -2 V to -4 V,  $D_{it}$  increased from ~1.2 × 10<sup>12</sup>/cm<sup>2</sup> eV to ~4 × 10<sup>12</sup>/cm<sup>2</sup> eV. The  $D_{it}$  of the HfO<sub>2</sub>/GaN device changed from 7.6 × 10<sup>12</sup>/cm<sup>2</sup> to 6.2 × 10<sup>12</sup>/cm<sup>2</sup> eV within the energy

FIG. 13. The calculated  $D_{it}$  of the Al<sub>2</sub>O<sub>3</sub>/m-plane GaN device and (b) HfO<sub>2</sub>/m-plane GaN device after annealing. In terms of  $D_{it}$ , both devices had comparable performance.

range from 0.25 eV to 0.51 eV. Both Al<sub>2</sub>O<sub>3</sub>/a-plane GaN and HfO<sub>2</sub>/a-plane GaN devices exhibited comparable interface characteristics.

A summary of the characterization results is given in Table I. For the device with  $Al_2O_3$  as a dielectric layer, the annealing process was beneficial to the reduction of  $N_{bt, tot}$ inside the oxide and  $D_{it}$  at the interface. In contrast, the annealing process, however, degenerated the interface of HfO<sub>2</sub>/GaN devices by increasing  $N_{bt, tot}$  and  $D_{it}$ . However, we need to note that the inadequate annealing process might also contribute to this degeneration. In addition, the annealing process removed the positive oxide charge, leading to a shift of the C-V curve towards the positive bias region. By comparing the polarity of GaN substrates, the a-plane GaN MOSCAPs always exhibited higher  $N_{bt}$ . tot and Dit than m-plane GaN MOSCAPs. Before annealing, HfO<sub>2</sub> grown on GaN had the lowest  $D_{it}$ . If the device was subjected to annealing, Al<sub>2</sub>O<sub>3</sub> grown on GaN could offer better quality of the interface. From these four devices, we can see that at room temperature, the lowest  $E_{it}$ was close to  $\sim 0.5 \,\text{eV}$  below the CBM. This value was comparable to the DFT model, which is  $\sim 0.7 \text{ eV}$  below CBM for m-plane GaN and  $\sim 0.5 \,\text{eV}$  for a-plane GaN.<sup>24</sup> Compared with the N<sub>bt, tot</sub> of Al<sub>2</sub>O<sub>3</sub>/c-plane GaN reported by Winzer et al.,<sup>34</sup> our Al<sub>2</sub>O<sub>3</sub>/m-plane GaN MOSCAPs showed low  $N_{bt, tot}$ , but it could be partially attributed to the voltage sweeping range because of the incapability of obtaining C-V curves at large positive bias due to the high leakage current.

TABLE I. Summary of the electrical characterization.

| Device<br>Annealing                                | Al <sub>2</sub> O <sub>3</sub> /m-plane GaN |          | HfO <sub>2</sub> /m-plane GaN |           | Al <sub>2</sub> O <sub>3</sub> /a-plane GaN | HfO <sub>2</sub> /a-plane GaN |

|----------------------------------------------------|---------------------------------------------|----------|-------------------------------|-----------|---------------------------------------------|-------------------------------|

|                                                    | Pre-                                        | Post-    | Pre-                          | Post-     | Post-                                       | Post-                         |

| $N_{bt, tot} (\times 10^{11} / \text{cm}^2)$       | 1.8                                         | 0.86     | 1.0                           | 1.9       | 2.7                                         | 4.3                           |

| $D_{it} (\times 10^{12} / \text{cm}^2 \text{ eV})$ | 5.0-2.5                                     | 2.5-1.9  | 2.0-0.7                       | 7.5-6.5   | 8.5-1.2                                     | 7.7-6.2                       |

| $E_{it} (eV)$                                      | 0.46-0.51                                   | 0.23-0.5 | 0.23-0.25                     | 0.27-0.35 | 0.23-0.48                                   | 0.25-0.52                     |

Without annealing, the  $D_{it}$  of the Al<sub>2</sub>O<sub>3</sub> MOSCAP in this work was higher than the  $D_{it}$  of the c-plane GaN device reported in literatures for  $E_c - E_{it} > 0.4 \,\text{eV}$  characterized by the conductance method ( $\sim 4 \times 10^{11}$ /cm<sup>2</sup> eV- $\sim 6 \times 10^{11}$ /cm<sup>2</sup> eV),<sup>34</sup> photo-assisted C-V method ( $\sim 1.5 \times 10^{11}$ /cm<sup>2</sup> eV),<sup>39</sup> and static C-V method ( $\sim 2 \times 10^{11}$ /cm<sup>2</sup> eV).<sup>40</sup> However, our  $D_{it}$  was comparable to the  $D_{it}$  of the c-plane GaN device reported in literatures for  $E_c - E_{it} > 0.4 \,\text{eV}$  characterized by deep level transient spectroscopy ( $\sim 3 \times 10^{11}$ /cm<sup>2</sup> eV- $\sim 8$  $\times 10^{11}$ /cm<sup>2</sup> eV).<sup>41</sup> With annealing at 500 °C in N<sub>2</sub> ambient, even though our devices showed a slight reduction of  $D_{it}$ within an  $E_{it}$  in the range of 0.2 eV-0.4 eV as observed in the literature,<sup>34</sup> our Al<sub>2</sub>O<sub>3</sub> MOSCAPs still revealed a high  $D_{it}$ compared to that of the Al<sub>2</sub>O<sub>3</sub>/c-plane GaN devices with annealing in  $N_2$  ambient for an  $E_{it}$  in the range of 0.2 eV-0.5 eV below the CBM characterized by the conductance method.<sup>34</sup> However, our Al<sub>2</sub>O<sub>3</sub> MOSCAPs showed a much lower  $D_{it}$  than Al<sub>2</sub>O<sub>3</sub>/c-plane GaN devices with N<sub>2</sub> annealing for an  $E_{it}$  in the range of 0.2 eV-0.5 eV below the CBM ( $>3 \times 10^{11}$ /cm<sup>2</sup> eV) characterized by constant capacitance deep level transient and optical spectroscopy reported by Long et al.<sup>41</sup> Compared to reported  $D_{it}$  at the Al<sub>2</sub>O<sub>3</sub>/mplane GaN interface  $(\sim 1.5 \times 10^{12}/\text{cm}^2 \text{ eV} \text{ for } 0.2 \text{ eV}-0.5 \text{ eV}$ below the CBM<sup>18,42</sup>), our post-annealed device showed a similar  $D_{it}$ . The effect of annealing on Al<sub>2</sub>O<sub>3</sub>/non-polar GaN is similar to its effect on the Al<sub>2</sub>O<sub>3</sub>/Si device.<sup>43</sup> In our experiment, the m-plane GaN devices exhibited similar interface properties compared to c-plane GaN devices.

For the HfO<sub>2</sub> MOSCAP, our results were slightly better than the reported HfO<sub>2</sub>/c-plane GaN device<sup>44,45</sup> even with the annealing process. After annealing, at positive bias, the leakage current and conductance increased significantly. The degraded insulting properties of oxide can be partially caused by the oxygen vacancies in the oxide.<sup>34</sup> Additionally, we cannot rule out the impacts of Ga native oxide regrowth at the interface and the metal dangling bonds close to the conduction band on the increase in interface states. Contrary to our observation, a reduction of  $D_{it}$  was observed at the sputtered HfO2/c-plane GaN interface46 and HfO2/Si with the interfacial layer47 after N2 annealing. The degree of reduction depends on the annealing atmosphere and temperature. Although the vacuum annealing improved the dielectric constant ( $\sim$ 25), it appeared that the annealing process also introduced interface traps. On a-plane GaN, in terms of  $D_{it}$ , the HfO<sub>2</sub> device had a slightly lower value than Al<sub>2</sub>O<sub>3</sub>, but the difference was insignificant. However, this difference was prone to be opposite on m-plane GaN. In fact, due to the ignored resistance during the calculation of the conductance peak  $(G_p/\omega)$ , the resultant  $D_{it}$  could be overestimated or underestimated. It also has been demonstrated that the annealing condition has significant influence on the interface properties in terms of  $D_{ii}$ . In order to optimize the interface, an appropriate condition should be used.

#### **IV. SUMMARY**

In summary, we characterized the interface properties of ALD-dielectrics/non-polar GaN. The MOSCAPs that were fabricated on a-plane and m-plane GaN substrates with Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub> as a dielectric layer were used for the electrical characterization. The impact of annealing on the density of border traps and the density of interface traps was investigated. The density of interface traps was extracted by the ac conductance method. Prior to annealing, the density of interface traps was in the magnitude of  $10^{12}$ , and it was one order higher than the lowest reported  $D_{it}$ . Although the annealing process brought down the  $D_{it}$  of Al<sub>2</sub>O<sub>3</sub> devices as expected in literatures,  $D_{it}$  was still higher than the best value. Further optimization on the process, including but not limited to the optimization of annealing conditions and the reduction of the series resistance, may be required to reduce  $D_{it}$ . By reducing leakage current, an accurate Cox can be obtained and the interface traps close to the conduction band can be accessed. Temperature dependent measurements can be conducted in order to extract  $D_{it}$  located close to mid-gap.

#### ACKNOWLEDGMENTS

This work was supported by the ONR grant (No. N000141310214) monitored by Dr. Paul A. Maki and by the Innovative Micro-Programs Accelerating Collaboration in Themes (IMPACT) program funded by the Office of Vice President of Research and Economic Development at the University at Buffalo. A portion of this work was performed in the UB shared instrumentation facility.

- <sup>1</sup>J. F. Muth, J. H. Lee, I. K. Shmagin, R. M. Kolbas, H. C. Casey, B. P. Keller, U. K. Mishra, and S. P. DenBaars, Appl. Phys. Lett. **71**, 2572 (1997).

- <sup>2</sup>D. C. Look, D. C. Reynolds, J. W. Hemsky, J. R. Sizelove, R. L. Jones, and R. J. Molnar, Phys. Rev. Lett. **79**, 2273 (1997).

- <sup>3</sup>Y. F. Wu, B. P. Keller, S. Keller, D. Kapolnek, P. Kozodoy, S. P. Denbaars, and U. K. Mishra, Appl. Phys. Lett. **69**, 1438 (1996).

- <sup>4</sup>S. Pimputkar, J. S. Specl, S. P. DenBaars, and S. Nakamura, Nat. Photonics 3, 180 (2009).

- <sup>5</sup>J. Chen, S. Loeb, and J.-H. Kim, Environ. Sci.: Water Res. Technol. **3**, 188 (2017).

- <sup>6</sup>E. T. Yu, X. Z. Dang, P. M. Asbeck, S. S. Lau, and G. J. Sullivan, J. Vac. Sci. Technol. B **17**, 1742 (1999).

- <sup>7</sup>C. Wetzel, M. Zhu, J. Senawiratne, T. Detchprohm, P. D. Persans, L. Liu, E. A. Preble, and D. Hanser, J. Cryst. Growth **310**, 3987 (2008).

- <sup>8</sup>Y. Fang, Z. Feng, J. Yin, X. Zhou, Y. Wang, G. Gu, X. Song, Y. Lv, C. Li, and S. Cai, IEEE Trans. Electron Devices **61**, 4084 (2014).

- <sup>9</sup>B. Reuters, A. Wille, N. Ketteniss, H. Hahn, B. Holländer, M. Heuken, H. Kalisch, and A. Vescan, J. Electron. Mater. **42**, 826 (2013).

- <sup>10</sup>S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, Appl. Phys. Lett. **94**, 062107 (2009).

- <sup>11</sup>G. Li, W. Wang, W. Yang, Y. Lin, H. Wang, Z. Lin, and S. Zhou, Rep. Prog. Phys. **79**, 056501 (2016).

- <sup>12</sup>V. Ramachandran, R. M. Feenstra, W. L. Sarney, L. Salamanca-Riba, J. E. Northrup, L. T. Romano, and D. W. Greve, Appl. Phys. Lett. **75**, 808 (1999).

- <sup>13</sup>S. Pezzagna, P. Vennéguès, N. Grandjean, and J. Massies, J. Cryst. Growth 269, 249 (2004).

- <sup>14</sup>M. McLaurin, T. E. Mates, F. Wu, and J. S. Speck, J. Appl. Phys. 100, 063707 (2006).

- <sup>15</sup>M. C. Schmidt, K.-C. Kim, R. M. Farrell, D. F. Feezell, D. A. Cohen, M. Saito, K. Fujito, J. S. Speck, S. P. DenBaars, and S. Nakamura, Jpn. J. Appl. Phys., Part 2 46, L190 (2007).

- <sup>16</sup>A. Chakraborty, B. A. Haskell, S. Keller, J. S. Speck, S. P. Denbaars, S. Nakamura, and U. K. Mishra, Jpn. J. Appl. Phys., Part 2 44, L173 (2005).

- <sup>17</sup>M. Ishida, M. Kuroda, T. Ueda, and T. Tanaka, Semicond. Sci. Technol. **27**, 024019 (2012).

- <sup>18</sup>T. Fujiwara, R. Yeluri, D. Denninghoff, J. Lu, S. Keller, J. S. Speck, S. P. DenBaars, and U. K. Mishra, Appl. Phys. Express 4, 096501 (2011).

- <sup>19</sup>S.-H. Park, Jpn. J. Appl. Phys., Part 1 39, 3478 (2000).

- <sup>20</sup>T. Paskova, Nitrides with Nonpolar Surfaces: Growth, Properties, and Device (Wiley, 2008), p. 23.

- <sup>21</sup>M. Kuroda, H. Ishida, T. Ueda, and T. Tanaka, J. Appl. Phys. **102**, 093703 (2007).

- <sup>22</sup>G. Li, W. Wang, W. Yang, and H. Wang, Surf. Sci. Rep. 70, 380 (2015).

- <sup>23</sup>W. Yang, W. Wang, Y. Lin, Z. Liu, S. Zhou, H. Qian, F. Gao, S. Zhang, and G. Li, J. Mater. Chem. C 2, 801 (2014).

<sup>24</sup>C. G. Wulls and D. Sterre L. April. Phys. 101, 081704 (2007).

- <sup>24</sup>C. G. Van de Walle and D. Segev, J. Appl. Phys. **101**, 081704 (2007).

- <sup>25</sup>Y. Jia, J. S. Wallace, E. Echeverria, J. A. Gardella, and U. Singisetti, Phys. Status Solidi B 254, 1600681 (2017).

- <sup>26</sup>L. S. McCarthy, P. Kozodoy, M. J. W. Rodwell, S. P. DenBarrs, and U. K. Mishra, IEEE Electron Device Lett. **20**, 277 (1999).

- <sup>27</sup>J.-O. Song, D.-S. Leem, S.-H. Kim, J. S. Kwak, O. H. Nam, Y. Park, and T.-Y. Seong, Solid-State Electron. 48, 1597 (2004).

- <sup>28</sup>D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, in 2016 International Electron Devices Meeting (IEDM), 10.1.1 (2016).

- <sup>29</sup>J. Kavalieros, B. Doyle, S. Datta, G. Dewey, M. Doczy, B. Jin, D. Lionberger, M. Metz, W. Rachmady, M. Radosavljevic, U. Shah, N. Zelick, and R. Chau, Symp. VLSI Technol. Dig. Tech. Papers 50 (2006).

- <sup>30</sup>J. B. Clemens, E. A. Chagarov, M. Holland, R. Droopad, J. Shen, and A. C. Kummel, J. Chem. Phys. **133**, 154704 (2010).

- <sup>31</sup>N. Goel, P. Majhi, C. O. Chui, W. Tsai, D. Choi, and J. S. Harris, Appl. Phys. Lett. 89, 163517 (2006).

- <sup>32</sup>H. Zhang, D. Chiappe, J. Meersschaut, T. Conard, A. Franquet, T. Nuytten, M. Mannarino, I. Radu, W. Vandervorst, and A. Delabie, J. Chem. Phys. **146**, 052810 (2017).

- <sup>33</sup>H. Liu and P. D. Ye, IEEE Electron Device Lett. **33**, 546 (2012).

- <sup>34</sup>A. Winzer, N. Szabó, A. Wachowiak, P. M. Jordan, J. Heitmann, and T.

- Mikolajick, J. Vac. Sci. Technol. B **33**, 01A106 (2015). <sup>35</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, J. Appl. Phys. **108**, 124101 (2010).

- <sup>36</sup>T. T. Duc, G. Pozina, E. Janzen, and C. Hemmingsson, J. Appl. Phys. **114**, 153702 (2013).

- <sup>37</sup>Z. Fan, S. N. Mohammad, W. Kim, O. Z. R. Aktas, A. E. Botchkarev, and H. Morkoc, Appl. Phys. Lett. 68, 1672 (1996).

- <sup>38</sup>D. K. Schroder, Semiconductor Material and Device Characterization (Wiley-Interscience, 2006), p. 349.

- <sup>39</sup>Y. Q. Wu, T. Shen, P. D. Ye, and G. D. Wilk, Appl. Phys. Lett. 90, 143504 (2007).

- <sup>40</sup>K. Ooyama, M. Miczek, and T. Hashizume, Jpn. J. Appl. Phys., Part 1 47, 5426 (2008).

- <sup>41</sup>R. D. Long, C. M. Jackson, J. Yang, A. Hazeghi, C. Hitzman, S. Majety, A. R. Archart, Y. Nishi, T. P. Ma, S. A. Ringel, and P. C. McIntyre, Appl. Phys. Lett. **103**, 201607 (2013).

- <sup>42</sup>X. Wu, R. Liang, L. Guo, L. Liu, L. Xiao, S. Shen, J. Xu, and J. Wang, Appl. Phys. Lett. **109**, 232101 (2016).

- <sup>43</sup>J. Benick, A. Richter, T. T. A. Li, N. E. Grant, K. R. McIntosh, Y. Ren, K. J. Weber, M. Hermle, and S. W. Glunz, in 2010 35th IEEE Photovoltaic Specialists Conference (PVSC) (2010), p. 000891.

- <sup>44</sup>Y. C. Chang, M. L. Huang, Y. H. Chang, Y. J. Lee, H. C. Chiu, J. Kwo, and M. Hong, Microelectron. Eng. **88**, 1207 (2011).

- <sup>45</sup>Y. C. Chang, H. C. Chiu, Y. J. Lee, M. L. Huang, K. Y. Lee, M. Hong, Y. N. Chiu, J. Kwo, and Y. H. Wang, Appl. Phys. Lett. **90**, 232904 (2007).

- <sup>46</sup>C. F. Shih, K. T. Hung, C. Y. Hsiao, S. C. Shu, and W. M. Li, J. Alloys Compd. **480**, 541 (2009).

- <sup>47</sup>M. Schmidt, M. C. Lemme, H. Kurz, T. Witters, T. Schram, K. Cherkaoui, A. Negara, and P. K. Hurley, Microelectron. Eng. 80, 70 (2005).